# Lecture 1

# Introduction, Concepts and laws of Boolean algebra

#### Introduction

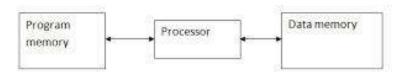

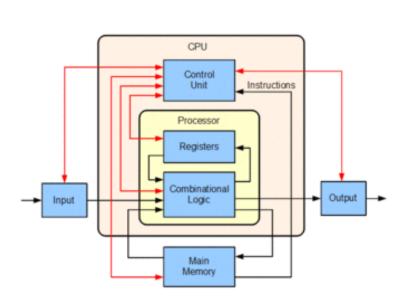

A digital computer stores data in terms of digits (numbers) and proceeds in discrete steps from one state to the next. The states of a digital computer typically involve binary digits which may take the form of the presence or absence of magnetic markers in a storage medium, on-off switches or relays. In digital computers, even letters, words and whole texts are represented digitally.

Digital Logic is the basis of electronic systems, such as computers and cell phones. Digital Logic is rooted in binary code, a series of zeroes and ones each having an opposite value. This system facilitates the design of electronic circuits that convey information, including logic gates. Digital Logic gate functions include and, or and not. The value system translates input signals into specific output. Digital Logic facilitates computing, robotics and other electronic applications.

Digital Logic Design is foundational to the fields of electrical engineering and computer engineering. Digital Logic designers build complex electronic components that use both electrical and computational characteristics. These characteristics may involve power, current, logical function, protocol and user input. Digital Logic Design is used to develop hardware, such as circuit boards and microchip processors. This hardware processes user input, system protocol and other data in computers, navigational systems, cell phones or other high-tech systems.

## **Boolean Algebra**

One of the primary requirements when dealing with digital circuits is to find ways to make them as simple as possible. This constantly requires that complex logical expressions be reduced to simpler expressions that nevertheless produce the same results under all possible conditions. The simpler expression can then be implemented with a smaller, simpler circuit, which in turn saves the price of the unnecessary gates, reduces the number of gates needed, and reduces the power and the amount of space required by those gates. One tool to reduce logical expressions is the mathematics of logical expressions, introduced by George Boole in 1854 and known today as *Boolean Algebra*. The rules of Boolean Algebra are simple and straight-forward, and can be applied to any logical expression. The resulting reduced expression can then be readily tested with a Truth Table, to verify that the reduction was valid. Boolean algebra is an algebraic structure defined on a set of elements B, together with two binary operators(+, .) provided the following postulates are satisfied.

1. Closure with respect to operator + and Closure with respect to operator .

2. An identity element with respect to + designated by 0: X+0=0+X=X

An identity element with respect to . designated by 1: X.1=1.X=X

3. Commutative with respect to +: X=Y=Y+X

Commutative with respect to .: X.Y=Y.X 4. .

distributive over +: X.(Y+Z)=X.Y+X.Z

+ distributive over :: X+(Y.Z)=(X+Y).(X+Z)

# 5. For every element x belonging to B, there exist an element x' or called the complement of x such that x. x'=0 and x+x'=1 x

#### 6. There exists at least two elements x,y belonging to B such that x≠y

The two valued Boolean algebra is defined on a set  $B = \{0,1\}$  with two binary operators + and.

| 1 | 1 |     |   | 1 |     |   |   |            |

|---|---|-----|---|---|-----|---|---|------------|

| Х | У | x.y | Х | Y | x+y |   | Х | <b>X</b> ′ |

| 0 | 0 | 0   | 0 | 0 | 0   |   | 0 | 1          |

| 0 | 1 | 0   | 0 | 1 | 1   |   | 1 | 0          |

| 1 | 0 | 0   | 1 | 0 | 1   | - |   |            |

| 1 | 1 | 1   | 1 | 1 | 0   |   |   |            |

Closure. from the tables, the result of each operation is either 0 or 1 and 1,0 belongs to B

Identity. From the truth table we see that 0 is the identity element for + and 1 is the identity element for .

Commutative law is obvious from the symmetry of binary operators table.

Distributive Law. x.(y+z)=x.y+x.z

| Х | у | Z | y+z | x.(y+z) | x.y | X.Z | x.y+x.z |

|---|---|---|-----|---------|-----|-----|---------|

| 0 | 0 | 0 | 0   | 0       | 0   | 0   | 0       |

| 0 | 0 | 1 | 1   | 0       | 0   | 0   | 0       |

| 0 | 1 | 0 | 1   | 0       | 0   | 0   | 0       |

| 0 | 1 | 1 | 1   | 0       | 0   | 0   | 0       |

| 1 | 0 | 0 | 0   | 0       | 0   | 0   | 0       |

| 1 | 0 | 1 | 1   | 1       | 0   | 1   | 1       |

| 1 | 1 | 0 | 1   | 1       | 1   | 0   | 1       |

| 1 | 1 | 1 | 1   | 1       | 1   | 1   | 1       |

Distributive of + over . can be shown as in the truth table above

#### From the complement table we can see that x+ x'=1 i.e 1+0=1 and x. x'=0 i.e 1.0=0

Principle of duality of Boolean algebra

The principle of duality state that every algebraic expression which can be deduced from the postulates of Boolean algebra remains valid if the operators and the identity elements are interchanged. This mean

that the dual of an expression is obtained changing every AND(.) to OR(+), every OR(+) to AND(.) and all 1's to 0's and vice-versa

#### Laws of Boolean algebra

**Postulate 2:**

(a) 0 + A = A (b)  $1 \cdot A = A$

Postulate 5 :

(a) A + A' = 1 (b)  $A \cdot A' = 0$

**Theorem1 : Identity Law**

(a) A + A = A (b) A A = A

Theorem2

(a) 1 + A = 1 (b) 0. A = 0

**Theorem3: involution**

*A''*=A

**Postulate 3: Commutative Law**

(a) A + B = B + A (b) A B = B A

**Theorem4: Associate Law**

(a) (A + B) + C = A + (B + C) (b) (A B) C = A (B C)

#### **Postulate4: Distributive Law**

(a)

$$A (B + C) = A B + A C$$

(b)  $A + (B C) = (A + B) (A + C)$

# Lecture 2

# **Boolean functions and Representation in SOP and POS forms**

#### **Boolean functions**

Operations of binary variables can be described by mean of appropriate mathematical function called Boolean function. A Boolean function define a mapping from a set of binary input values into a set of output values. A Boolean function is formed with binary variables, the binary operators AND and OR and the unary operator NOT.

For example , a Boolean function  $f(x_1, x_2, x_3, \dots, x_n) = y$  defines a mapping from an arbitrary combination of binary input values  $(x_1, x_2, x_3, \dots, x_n)$  into a binary value y. a binary function with n input variable can operate on  $2^n$  distincts values. Any such function can be described by using a truth table consisting of  $2^n$  rows and n columns. The content of this table are the values produced by that function when applied to all the possible combination of the n input variable.

Example

| х | у | x.y |

|---|---|-----|

| 0 | 0 | 0   |

| 0 | 1 | 0   |

| 1 | 0 | 0   |

| 1 | 1 | 1   |

The function f, representing x.y, that is f(x,y)=xy. Which mean that f=1 if x=1 and y=1 and f=0 otherwise.

For each rows of the table, there is a value of the function equal to 1 or 0. The function f is equal to the sum of all rows that gives a value of 1.

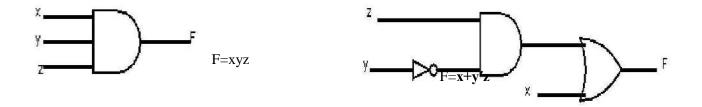

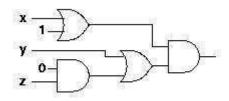

A Boolean function may be transformed from an algebraic expression into a logic diagram composed of AND, OR and NOT gate. When a Boolean function is implemented with logic gates, each literal in the function designates an input to a gate and each term is implemented with a logic gate . e.g.

## **Standard form**

Another way to express a boolean function is in saturd form. Here the term that form the function may contains one, two or nay number of literals. There are two types of standard form. The **sum of product** (SOP) and the **product of sum (POS)**.

The sum of product(SOP) is a Boolean expression containing AND terms called product term of one or more literals each. The sum denotes the ORing of these terms

e.g. F=x+xy'+x'yz

the product of sum (POS) is a Boolean expression containing OR terms called SUM terms. Each term may have any number of literals. The product denotes the ANDing of these terms

e.g. F = x(x+y')(x'+y+z)

a boolean function may also be expressed in a non standard form. In that case, distributive law can be used to remove the parenthesis

F=(xy+zw)(x'y'+z'w') = xy(x'y'+z'w')+zw(x'y'+z'w') =Xyx'y +xyz'w' +zwx'y' +zwz'w'

=xyz'w'+zwx'y'

A Boolean equation can be reduced to a minimal number of literal by algebraic manipulation. Unfortunately, there are no specific rules to follow that will guarantee the final answer. The only methods is to use the theorem and postulate of Boolean algebra and any other manipulation that becomes familiar.

## Describing existing circuits using Logic expressions

To define what a combinatorial circuit does, we can use a *logic expression* or an *expression* for short. Such an expression uses the two constants 0 and 1, variables such as x, y, and z (sometimes with suffixes) as names of inputs and outputs, and the operators +,  $\cdot$  and a horizontal bar or a prime (which stands for *not*). As usual, multiplication is considered to have higher priority than addition. Parentheses are used to modify the priority.

If Boolean functions in either Sum of Product or Product of Sum forms can be implemented using 2-

Level implementations.

For SOP forms AND gates will be in the first level and a single OR gate will be in the second level. For POS forms OR gates will be in the first level and a single AND gate will be in the second level.

#### **Examples:**

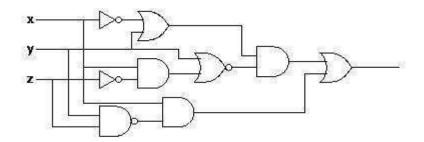

#### (X'+Y)(Y+XZ')'+X(YZ)'

The equation is neither in sum of product nor in product of sum. The implementation is as follow

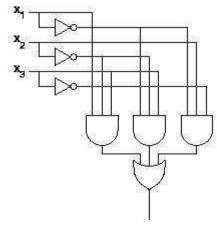

#### X1X2'X3+X1'X2'X2+X1'X2X'3

The equation is in sum of product. The implementation is in 2-Levels. AND gates form the first level and a single OR gate the second level.

#### (X+1)(Y+0Z)

The equation is neither in sum of product nor in product of sum. The implementation is as follow

# Lecture 3

# Minterm and maxterm , Minimization of logic expressions by Karnaugh Map

#### Canonical form (Minterns and Maxterms)

A binary variable may appear either in it normal form or in it complement form . consider two binary variables x and y combined with AND operation. Since each variable may appears in either form there are four possible combinations: x'y', x'y, xy',xy. Each of the term represent one distinct area in the

Venn diagram and is called minterm or a standard product. With n variable, 2<sup>n</sup> minterms can be formed.

In a similar fashion, n variables forming an OR term provide 2<sup>n</sup> possible combinations called maxterms or standard sum. Each maxterm is obtained from an OR term of the n variables, with each variable being primed if the corresponding bit is 1 and un-primed if the corresponding bit is 0. Note that each maxterm is the complement of its corresponding minterm and vice versa.

| Х | Y | Ζ | Minterm | maxterm  |

|---|---|---|---------|----------|

| 0 | 0 | 0 | x'y'z'  | X+y+z    |

| 0 | 0 | 1 | X'y'z   | X+y+z'   |

| 0 | 1 | 0 | X'yz'   | X+y'+z   |

| 0 | 1 | 1 | X'yz    | X+y'+z'  |

| 1 | 0 | 0 | Xy'z'   | X'+y+z   |

| 1 | 0 | 1 | Xy'z    | X'+y+z'  |

| 1 | 1 | 0 | Xyz'    | X'+y'+z  |

| 1 | 1 | 1 | Xyz     | X'+y'+z' |

A Boolean function may be expressed algebraically from a given truth table by forming a minterm for each combination of variable that produce a 1 and taken the OR of those terms.

Similarly, the same function can be obtained by forming the maxterm for each combination of variable that produces 0 and then taken the AND of those term.

It is sometime convenient to express the bolean function when it is in sum of minterms, in the following notation:

#### $F(X,Y,Z) = \sum (1,4,5,6,7)$ . the summation symbol $\sum$ stands for the ORing of the terms; the number

follow ing it are the minterms of the function. The letters in the parenthesis following F form list of the variables in the order taken when the minterm is converted to an AND term.

#### So, $F(X,Y,Z) = \sum (1,4,5,6,7) = X'Y'Z + XY'Z' + XY'Z + XYZ' + XYZ$

Sometime it is convenient to express a Boolean function in its sum of minterm. If it is not in that case, the expression is expanded into the sum of AND term and if there is any missing variable, it is **ANDed with an expression such as x+x' where x is one of** the missing variable.

To express a Boolean function as a product of maxterms, it must first be brought into a form of OR terms. This can be done by using distributive law x+xz=(x+y)(x+z). then if there is any missing variable, say x in each OR term is ORded with xx'.

#### e.g. represent F=xy+x'z as a product of maxterm

```

=(xy + x')(xy+z)

(x+x')(y+x')(x+z)(y+z)

(y+x')(x+z)(y+z)

Adding missing variable in each term

(y+x')= x'+y+zz' =(x'+y+z)(x'+y+z')

(x+z)= x+z+yy' =(x+y+z)(x+y'+z)

```

```

(y+z)= y+z+xx' =( x+y+z)( x'+y+z)

F=( x+y+z)( x+y'+z) ( x'+y+z)(

x'+y+z')

```

A convenient way to express this function is as follow :

$F(x,y,z) = \prod (0,2,4,5)$

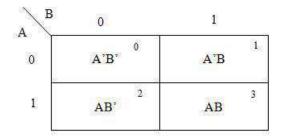

#### Karnaugh map

The Karnaugh map also known as Veitch diagram or simply as K map is a two dimensional form of the truth table, drawn in such a way that the simplification of Boolean expression can be immediately **be seen from the location of 1's in the map. The map is a diagram made up of squares , each sqare** represent one minterm. Since any Boolean function can be expressed as a sum of minterms, it follows that a Boolean function is recognised graphically in the map from the area enclosed by those squares whose minterms are included in the function.

A two variable Boolean function can be represented as follow

A three variable function can be represented as follow

| X          | 00     | 01°   | 11   | 10    |

|------------|--------|-------|------|-------|

| ,0)<br>,0) | x'y'z' | x'y'z | x'yz | x'yz' |

| 1          | xy'z'  | ×ý′z  | хуг  | ×yz'  |

A four variable Boolean function can be represented in the map bellow

|   |    |      | A  | В    |    |          |           |

|---|----|------|----|------|----|----------|-----------|

|   | 1  | 00   | 01 | 11   | 10 |          |           |

|   | 8  | 0    | 4  | 32   | 8  | ABCD     | ABCD      |

|   | 8  | ្លប  | 4  | 12   | 8  | 0000 - 0 | 1000 - B  |

|   | 3  | - 25 | 52 | 3558 |    | 0001 - 1 | 1001 - 9  |

| 0 | 8  | 1    | 5  | 13   | 9  | 0010 - 2 | 1010 - 10 |

| 9 | U  |      |    |      |    | 0011 - 3 | 1011 - 11 |

|   | 8  | 3    | 7  | 15   | 11 | 0100 - 4 | 1100 - 12 |

|   | ł  |      |    | -    |    | 0101 - 5 | 1101 - 13 |

|   | 9  | 2    | 6  | 14   | 10 | 0110 - 6 | 1110 - 14 |

|   | ્ય |      |    |      |    | 0111 - 7 | 1111 - 15 |

To simplify a Boolean function using karnaugh map, the first step is to plot all ones in the **function truth table on the map. The next step is to combine adjacent 1's into a group of one, two, four,**

eight, sixteen. The group of minterm should be as large as possible. A single group of four minterm yields a simpler expression than two groups of two minterms.

In a four variable karnaugh map,

- 1 variable product term is obtained if 8 adjacent squares are covered

- 2 variable product term is obtained if 4 adjacent squares are covered

- 3 variable product term is obtained if 2 adjacent squares are covered

- 1 variable product term is obtained if 1 square is covered

A square having a 1 may belong to more than one term in the sum of product expression

The final stage is reached when each of the group of minterms are ORded together to form the simplified sum of product expression

The karnaugh map is not a square or rectangle as it may appear in the diagram. The top edge is adjacent to the bottom edge and the left hand edge adjacent to the right hand edge. Consequent, two squares in karnaugh map are said to be adjacent if they differ by only one variable

## Minimization of Boolean expressions using Karnaugh maps.

Given the following truth table for the majority function.

| а | b | С | M(output) |

|---|---|---|-----------|

| 0 | 0 | 0 | 0         |

| 0 | 0 | 1 | 0         |

| 0 | 1 | 0 | 0         |

| 0 | 1 | 1 | 1         |

| 1 | 0 | 0 | 0         |

| 1 | 0 | 1 | 1         |

| 1 | 1 | 0 | 1         |

| 1 | 1 | 1 | 1         |

The Boolean algebraic expression is

m = a'bc + ab'c + abc' + abc.

the minimization using algebraic manipulation can be done as follows.

m = a'bc + abc + ab'c + abc + abc' + abc

= (a' + a)bc + a(b' + b)c + ab(c' + c)

= bc + ac + ab

The **abc** term was replicated and combined with the other terms.

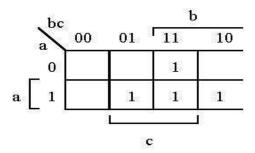

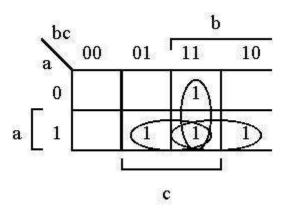

To use a Karnaugh map we draw the following map which has a position (square) corresponding to each of the 8 possible combinations of the 3 Boolean variables. The upper left position corresponds to the 000 row of the truth table, the lower right position corresponds to 110. Each square has two coordinates, the vertical coordinate corresponds to the value of variable  $\mathbf{a}$  and the horizontal corresponds to the values of  $\mathbf{b}$  and  $\mathbf{c}$ .

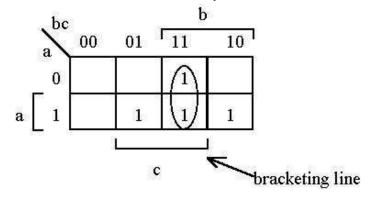

The 1s are in the same places as they were in the original truth table. The 1 in the first row is at position 110 ( $\mathbf{a} = 1$ ,  $\mathbf{b} = 1$ ,  $\mathbf{c} = 0$ ). The minimization is done by drawing circles around sets of adjacent 1s.

Adjacency is horizontal, vertical, or both. The circles must always contain  $2^{n}$  1s where n is an integer.

We have circled two 1s. The fact that the circle spans the two possible values of  $\mathbf{a}$  (0 and 1) means that the  $\mathbf{a}$  term is eliminated from the Boolean expression corresponding to this circle. The bracketing lines shown above correspond to the positions on the map for which the given variable has the value 1. The bracket delimits the set of squares for which the variable has the value 1. We see that the two circled 1s are at the intersection of sets  $\mathbf{b}$  and  $\mathbf{c}$ , this means that the Boolean expression for this set of bc.

Now we have drawn circles around all the 1s. The left bottom circle is the term **ac**. Note that the circle spans the two possible values of **b**, thus eliminating the **b** term. Another way to think of it is that the set of squares in the circle contains the same squares as the set **a** intersected with the set **c**. The other circle (lower right) corresponds to the term **ab**. Thus the expression reduces to

bc + ac + ab as we saw before.

What is happening? What does adjacency and grouping the 1s together have to do with minimization? Notice that the 1 at position 111 was used by all 3 circles. This 1 corresponds to the abc term that was replicated in the original algebraic minimization. Adjacency of 2 1s means that the terms corresponding to those 1s differ in one variable only. In one case that variable is negated and in the other it is not.

For example, in the first map above, the one with only 1 circle. The upper 1 is the term  $\mathbf{a'bc}$  and the lower is **abc**. Obviously they combine to form **bc** ( $\mathbf{a'bc} + \mathbf{abc} = (\mathbf{a'} + \mathbf{a})\mathbf{bc} = \mathbf{bc}$ ). That is exactly what we got using the map.

The map is easier than algebraic minimization because we just have to recognize patterns of 1s in the map instead of using the algebraic manipulations. Adjacency also applies to the edges of the map.

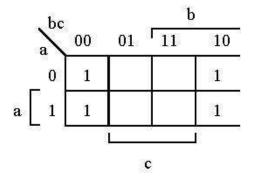

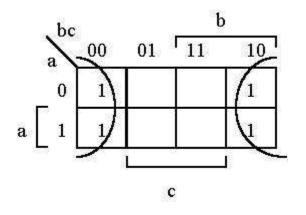

Let's try another 3 variable map.

At first it may seem that we have two sets, one on the left of the map and the other on the right. Actually there is only 1 set because the left and right are adjacent as are the top and bottom. The expression for all 4 1s is  $\mathbf{c}'$ . Notice that the 4 1s span both values of  $\mathbf{a}$  (0 and 1) and both values of  $\mathbf{b}$  (0 and 1). Thus, only the  $\mathbf{c}$  value is left. The variable  $\mathbf{c}$  is 0 for all the 1s, thus we have  $\mathbf{c}'$ . The other way to look at it is that the 1's overlap the horizontal  $\mathbf{b}$  line and the short vertical  $\mathbf{a}$  line, but they all lay outside the horizontal  $\mathbf{c}$  line, so they correspond to  $\mathbf{c}'$ . (The horizontal  $\mathbf{c}$  line delimits the  $\mathbf{c}$  set. The  $\mathbf{c}'$  set consists of all squares outside the  $\mathbf{c}$  set. Since the circle includes all the squares in  $\mathbf{c}'$ , they are defined by  $\mathbf{c}'$ . Again, notice that both values of  $\mathbf{a}$  and  $\mathbf{b}$  are spanned, thus eliminating those terms.)

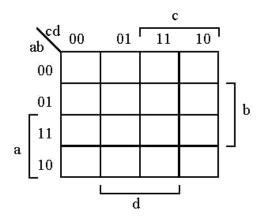

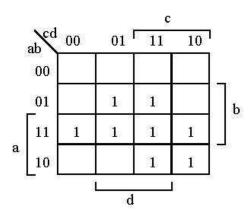

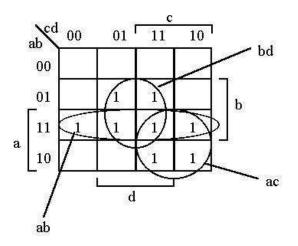

Now for 4 Boolean variables. The Karnaugh map is drawn as shown below.

The following corresponds to the Boolean expression

q = a'bc'd + a'bcd + abc'd' + abc'd + abcd + abcd' + ab'cd + ab'cd'

# RULE: Minimization is achieved by drawing the smallest possible number of circles, each

#### containing the largest possible number of 1s.

Grouping the 1s together results in the following.

The expression for the groupings above is

$$q = bd + ac + ab$$

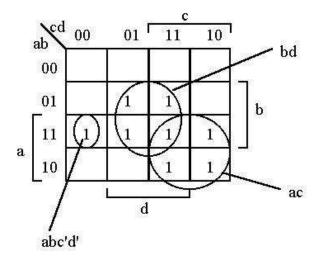

This expression requires 3 2-input **and** gates and 1 3-input **or** gate. We could have accounted for all the 1s in the map as shown below, but that results in a more complex expression requiring a more complex gate.

The expression for the above is bd + ac + abc'd'. This requires 2 2-input and gates, a 4-input and gate, and a 3 input or gate. Thus, one of the and gates is more complex (has two additional inputs) than required above. Two inverters are also needed.

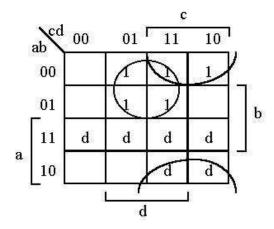

#### Don't Cares

Sometimes we do not care whether a 1 or 0 occurs for a certain set of inputs. It may be that those inputs will never occur so it makes no difference what the output is. For example, we might have a bcd (binary coded decimal) code which consists of 4 bits to encode the digits 0 (0000) through 9 (1001). The remaining codes (1010 through 1111) are not used. If we had a truth table for the prime numbers 0 through 9, it would be

|      | F |

|------|---|

| abcd | р |

| 0000 | 0 |

| 0001 | 1 |

| 0010 | 1 |

| 0011 | 1 |

| 0100 | 0 |

| 0101 | 1 |

| 0110 | 0 |

| 0111 | 1 |

| 1000 | 0 |

| 1001 | 0 |

| 1010 | d |

| 1011 | d |

| 1100 | d |

| 1101 | d |

| 1110 | d |

| 1111 | d |

The ds in the above stand for "don't care", we don't care whether a 1 or 0 is the value for that combination of inputs because (in this case) the inputs will never occur.

The circle made entirely of 1s corresponds to the expression **a'd** and the combined 1 and d circle (actually a combination of arcs) is **b'c**. Thus, if the disallowed input 1011 did occur, the output would be 1 but if the disallowed input 1100 occurs, its output would be 0. The minimized expression is

$$\mathbf{p} = \mathbf{a'd} + \mathbf{b'c}$$

Notice that if we had ignored the ds and only made a circle around the 2 1s, the resulting expression would have been more complex, **a'b'c** instead of **b'c**.

# Lecture 4 & Lecture 5

# Adder and Subtractor (half-full adder & subtractor)

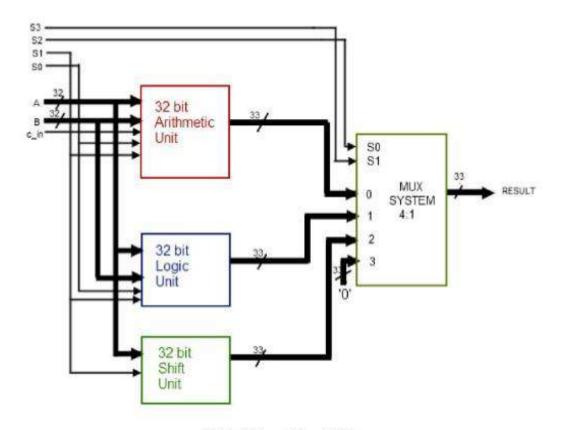

## Adders

In electronics, an adder or summer is a digital circuit that performs addition of numbers. In modern computers adders reside in the arithmetic logic unit (ALU) where other operations are performed. Although adders can be constructed for many numerical representations, such as Binary-coded decimal or excess-3, the most common adders operate on binary numbers. In cases where twos complement or ones complement is being used to represent negative numbers, it is trivial to modify an adder into an adder-subtracter. Other signed number representations require a more complex adder.

#### -Half Adder

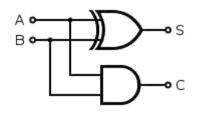

A half adder is a logical circuit that performs an addition operation on two binary digits. The half adder produces a sum and a carry value which are both binary digits.

A half adder has two inputs, generally labelled A and B, and two outputs, the sum S and carry C. S is the two-bit XOR of A and B, and C is the AND of A and B. Essentially the output of a half adder is the sum of two one-bit numbers, with C being the most significant of these two outputs.

The drawback of this circuit is that in case of a multibit addition, it cannot include a carry.

Following is the truth table for a half adder:

| A | В | Carry | Sum |

|---|---|-------|-----|

| 0 | 0 | 0     | 0   |

| 0 | 1 | 0     | 1   |

| 1 | 0 | 0     | 1   |

| 1 | 1 | 1     | 0   |

Equation of the Sum and Carry.

Sum=A'B+AB' Carry=AB One can see that Sum can also be implemented using XOR gate

(a) Truth Table of Half Adder

(b) Logic Diagram of Half Adder

#### Figure 1. (a) Truth Table and (b) Logic Diagram of Half Adder

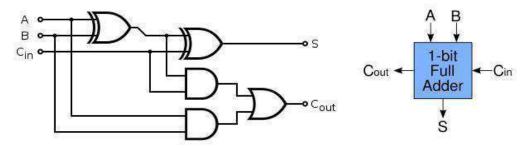

#### Full Adder.

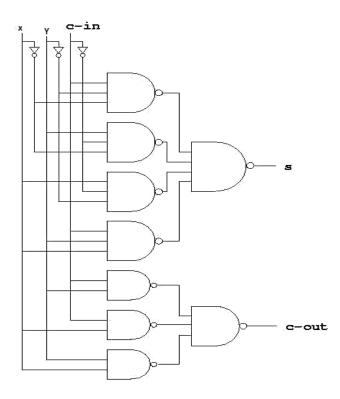

A full adder has three inputs A, B, and a carry in C, such that multiple adders can be used to add larger numbers. To remove ambiguity between the input and output carry lines, the carry in is labelled  $C_i$  or  $C_{in}$  while the carry out is labelled  $C_0$  or  $C_{out}$ .

A full adder is a logical circuit that performs an addition operation on three binary digits. The full adder produces a sum and carry value, which are both binary digits. It can be combined with other full adders or work on its own.

| Input |   |    | Output |   |  |

|-------|---|----|--------|---|--|

| Α     | В | Ci | Co     | S |  |

| 0     | 0 | 0  | 0      | 0 |  |

| 0     | 0 | 1  | 0      | 1 |  |

| 0     | 1 | 0  | 0      | 1 |  |

| 0     | 1 | 1  | 1      | 0 |  |

| 1     | 0 | 0  | 0      | 1 |  |

| 1     | 0 | 1  | 1      | 0 |  |

| 1     | 1 | 0  | 1      | 0 |  |

| 1     | 1 | 1  | 1      | 1 |  |

(a) Truth table of full adder

$C_0 = A'BC_i + AB'C_i + ABC_i' + ABC_i$

$S=A'B'C_i + A'BC_i' + ABC_i' + ABC_i$

A full adder can be trivially built using our ordinary design methods for combinatorial circuits. Here is the resultingcircuit diagram using NAND gates only:

(b) Logic Diagram Of full adder

$C_0 = A'BC_i + ABC_i + ABC_i$  by manipulating  $C_0$ , we can see that  $C_0 = C_i(A \oplus B) + AB$

S=A'B'C<sub>1</sub>+A'BC<sub>1</sub>'+ABC<sub>1</sub>'+ABC<sub>1</sub> By manipulating S, we can see that S=C<sub>1</sub>  $\bigoplus$  (A  $\bigoplus$ B)

Note that the final OR gate before the carry-out output may be replaced by an XOR gate without altering the resulting logic. This is because the only discrepancy between OR and XOR gates occurs when both inputs are 1; for the adder shown here, this is never possible. Using only two types of gates is convenient if one desires to implement the adder directly using common IC chips.

A full adder can be constructed from two half adders by connecting A and B to the input of one half adder, connecting the sum from that to an input to the second adder, connecting Ci to the other input and OR the two carry outputs. Equivalently, S could be made the three-bit xor of A, B, and Ci and Co could be made the three-bit majority function of A, B, and Ci. The output of the full adder is the two-bit arithmetic sum of three one-bit numbers.

Figure 2. Full Adder (a) Logic Diagram and (b) Graphic Diagram

# **Subtractor**

In electronics, a subtractor can be designed using the same approach as that of an adder. The binary subtraction process is summarized below. As with an adder, in the general case of calculations on multi-bit numbers, three bits are involved in performing the subtraction for each bit: the minuend (Xi), subtrahend (Yi), and a borrow in from the previous (less significant) bit order position (Bi). The outputs are the difference bit (Di) and borrow bit Bi + 1.

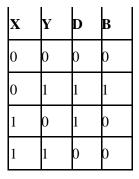

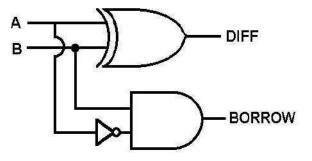

#### Half subtractor

The half-subtractor is a combinational circuit which is used to perform subtraction of two bits. It has two inputs, X (minuend) and Y (subtrahend) and two outputs D (difference) and B (borrow). Such a circuit is called a half -subtractor because it enables a borrow out of the current arithmetic operation but no borrow in from a previous arithmetic operation.

The truth table for the half subtractor is given below.

$\mathbf{D}=\mathbf{X'Y}+\mathbf{XY'} \quad \text{or } \mathbf{D}=\mathbf{X} \textcircled{*}$

#### B=X'Y

(a) Truth Table of half subtractor

(b) Logic Diagram of half subtractor

#### Figure 3. (a) Truth Table and (b) Logic Diagram of Half Subtractor

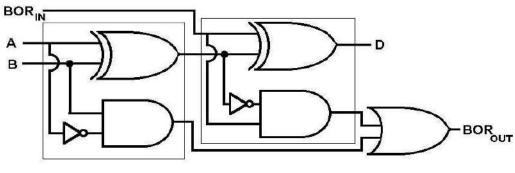

#### **Full Subtractor**

As in the case of the addition using logic gates, a *full subtractor* is made by combining two halfsubtractors and an additional OR-gate. A full subtractor has the borrow in capability (denoted as **BOR**<sub>IN</sub> in the diagram below) and so allows *cascading* which results in the possibility of **multi-bit subtraction**. The final truth table for a full subtractor looks like:

| Α | B | BORIN | D | BOR |

|---|---|-------|---|-----|

| 0 | 0 | 0     | 0 | 0   |

| 0 | 0 | 1     | 1 | 1   |

| 0 | 1 | 0     | 1 | 0   |

| 0 | 1 | 1     | 0 | 0   |

| 1 | 0 | 0     | 1 | 1   |

| 1 | 0 | 1     | 0 | 1   |

| 1 | 1 | 0     | 0 | 0   |

| 1 | 1 | 1     | 1 | 1   |

(a) Truth Table of half subtractor

Find out the equations of the borrow and the difference

The circuit diagram for a full subtractor is given below.

(b) Logic Diagram of full subtractor

Figure 4. (a) Truth Table and (b) Logic Diagram of Full Subtractor

For a wide range of operations many circuit elements will be required. A neater solution will be to use subtraction via addition using *complementing* as was discussed in the binary arithmetic topic. In this case only adders are needed as shown bellow.

# Lecture 6

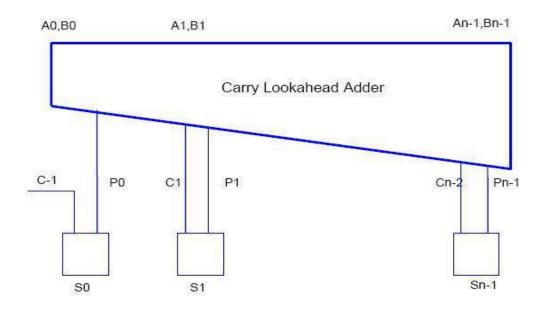

# <u>Carry look ahead adder and Parity Generator</u> Carry Look Ahead Adder

# The Carry Look Ahead removes the carry-ripple effect in the other types of adders described above. The architecture of a CLA is shown in Figure 5. Since the CLA generates a carry for each bit simultaneously, the delay is greatly reduced. The independent carry can be computed by expanding from equation 4:

$$C_{o,k} = G_k + P_k(G_{k-1} + P_{k-1}(\dots + P_1(G_0 + P_0Ci, 0)))$$

(10)

In practice, it is not possible to use the CLA to realize constant delay for the wider-bit adders since there will be a substantial loading capacitance, and hence larger delay and larger power consumption. The CLA has the fastest growing area requirements with respect to the bit size.

In practice, the mixture of architectures listed above are often used in the design of wider bit adders to realize better optimization in terms of design metrics such as performance, power consumption, Power-delay Product (PDP), Energy-delay Product (EDP), area, and noise margin, etc.

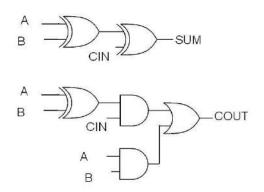

#### One Bit Full Adder:

The main objective of this phase is to get a logically minimized expression to evaluate the two required output from the three inputs of the single bit full adder.First the main functionality of the single bit adder can be modeled by the following table (see table1)

| Α | В | CIN | SU<br>M | CO<br>UT |

|---|---|-----|---------|----------|

| 0 | 0 | 0   | 0       | 0        |

| 0 | 0 | 1   | 1       | 0        |

| 0 | 1 | 0   | 1       | 0        |

| 0 | 1 | 1   | 0       | 1        |

| 1 | 0 | 0   | 1       | 0        |

| 1 | 0 | 1   | 0       | 1        |

| 1 | 1 | 0   | 0       | 1        |

| 1 | 1 | 1   | 1       | 1        |

Table 1 : One Bit Full Adder Truth Table

Using simple logic design and minimization techniques we can derive the following formula for our single bit full adder.

Sum = (A XOR B) XOR Cin

Cout =A . B + Cin . (A XOR B)

See the figure belowfor the gate implementation of this equation.

Figure 6: One bit Full Adder Logic Design

We can see clearly from **figure 1** that the critical path is the path from the input to the COUT. This gives us a clue for the path that we have to optimize during the circuit design phase. We have used (**Logic Works version 4.01**) to logically simulate the functionality of this adder. We applied the 8 test vectors shown above and ran the simulation for enough time. Finally we got the results witch matched the ones in **table1**.

#### Four Bit Full Adder:

Here is an important decision point which is affecting our design criteria. We need to choose the type of adder and the type of carry propagation we are going to use. There are two main categories of adders. Carry Look Ahead Adders and Carry Ripple Adders.

#### **Ripple Carry Adder**

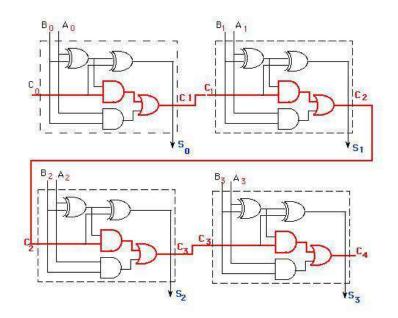

In this type of adders, the output carry from one block is connected to the carry input pin of the next block. So the carry will propagate serially through full adder blocks (see figure2). The main advantage of this approach is its ease of implementation (modularity) but it cost more delay since the critical path length now is proportional to the size of the adder (number of bits) (see figure2) critical path is in red color.

Figure 7: One bit Full Adder Logic Design

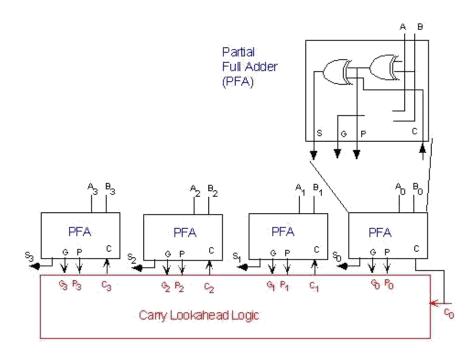

#### **Carry Look Ahead adder**

Carry look ahead adder depends on the idea of generating and propagating the carry. However the maximum delay for the curry now is 2 logic levels. See **figure 3** and **figure 4** for details.

Figure 8. Carry Look Ahead Adder (Logical design)

Where G, P and carry values are as follows :

$$\begin{split} G_i &= A_i.B_i \\ Pi &= (A_i \square B_i) \\ C_1 &= G_0 + P_0.C_0 \\ C_2 &= G_1 + P_1.C_1 = G_1 + P1.G_0 + P_1.P_0.C_0 \\ C_3 &= G_2 + P_2.G_1 + P_2.P_1.G_0 + P_2.P_1.P_0.C_0 \\ C_4 &= G_3 + P_3.G_2 + P_3.P_2.G_1 + P_3P_2.P_1.G_0 + P_3P_2.P_1.P_0.C_0 \end{split}$$

It is clear that the main advantage of Carry look a head adder is the delay reduction due to the Carry Look Ahead logic block. However it increases the area significantly as the number of bits increases .

Some other adder implementations also exists where different combinations of ripple and look ahead and other logic blocks are used.

# **Parity Generator**

# What is parity bit

The parity generating technique is one of the most widely used **error detection techniques** for the data transmission.

In digital systems, when binary data is transmitted and processed, data may be subjected to noise so that such noise can alter 0s (of data bits) to 1s and 1s to 0s.

Hence, **parity bit** is added to the word containing data in order to make number of 1s either even or odd. Thus it is used to detect errors, during the transmission of binary data. The message containing the data bits along with parity bit is transmitted from transmitter node to receiver node. At the receiving end, the number of 1s in the message is counted and if it doesn't match with the transmitted one, then it means there is an error in the data.

#### Parity Generator And Checker

A parity generator is a combinational logic circuit that generates the parity bit in the transmitter.

On the other hand, a circuit that checks the parity in the receiver is called parity checker. A combined circuit or devices of parity generators and parity checkers are commonly used in digital systems to detect the single bit errors in the transmitted data word.

The sum of the data bits and parity bits can be even or odd . In even parity, the added parity bit will make the total number of 1s an even amount whereas in odd parity the added parity bit will make the total number of 1s odd amount.

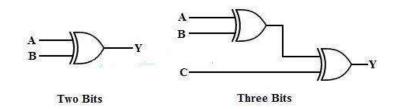

The basic principle involved in the implementation of parity circuits is that sum of odd number of 1s is always 1 and sum of even number of 1s is always zero. Such error detecting and correction can be implemented by using Ex-OR gates (since Ex-OR gate produce zero output when there are even number of inputs).

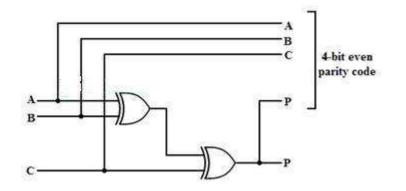

To produce two bits sum, one Ex-OR gate is sufficient whereas for adding three bits two Ex-OR gates are required as shown in below figure.

Figure 9: Ex-OR gatesParity Generator

It is combinational circuit that accepts an n-1 bit stream data and generates the additional bit that is to be transmitted with the bit stream. This additional or extra bit is termed as a parity bit. In **even parity** bit **scheme, the parity bit is '0' if there are even number of 1s** in the data stream and the **parity bit is '1' if** there are **odd number of 1s** in the data stream. In **odd parity** bit scheme, **the parity bit is '1' if there** are **even number of 1s** in the **data stream and the parity bit is '1'** if there are **even number of 1s** in the **data stream and the parity bit is '0' if there of 1s** in the **data stream and the parity bit is '0' if there are odd number of 1s** in the **data stream and the parity bit is '0' if there are odd number of 1s** in the data stream and the parity bit is '0' if there are odd number of 1s in the data stream and the parity bit is '0' if there are odd number of 1s in the data stream and odd parity generators.

#### **Even Parity Generator**

Let us assume that a 3-bit message is to be transmitted with an even parity bit. Let the three inputs A, B and C are applied to the circuits and output bit is the parity bit P. The total number of 1s must be even, to generate the even parity bit P.The figure below shows the truth table of even parity generator in which 1 is placed as parity bit in order to make all 1s as even when the number of 1s in the truth table is odd.

| 3- | bit messa | ge | Even parity bit generator (P) |  |  |  |  |

|----|-----------|----|-------------------------------|--|--|--|--|

| Α  | В         | С  | Ŷ                             |  |  |  |  |

| 0  | 0         | 0  | 0                             |  |  |  |  |

| 0  | 0         | 1  | 1                             |  |  |  |  |

| 0  | 1         | 0  | 1                             |  |  |  |  |

| 0  | 1         | 1  | 0                             |  |  |  |  |

| 1  | 0         | 0  | 1                             |  |  |  |  |

| 1  | 0         | 1  | 0                             |  |  |  |  |

| 1  | 1         | 0  | 0                             |  |  |  |  |

| 1  | 1         | 1  | 1                             |  |  |  |  |

Table 2. Even Parity Bit Generator

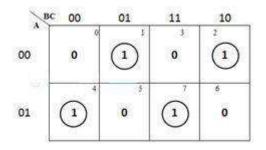

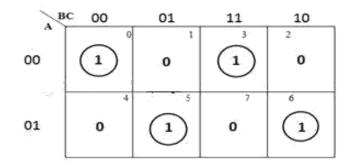

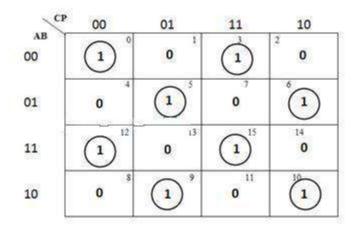

The K-map simplification for 3-bit message even parity generator is

#### Figure 10. k- map of even parity bit generator

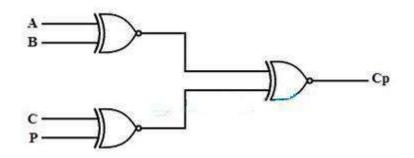

The logic diagram of even parity generator with two Ex - OR gates is shown below. The three bit message along with the parity generated by this circuit which is transmitted to the receiving end where

parity checker circuit checks whether any error is present or not. To generate the even parity bit for a 4-bit data, three Ex-OR gates are required to add the 4-bits and their sum will be the parity bit.

Figure 11. Circuit Diagram of even parity bit generator

#### **Odd Parity Generator**

Let us consider that the 3-bit data is to be transmitted with an odd parity bit. The three inputs are A, B and C and P is the output parity bit. The total number of bits must be odd in order to generate the odd parity bit. In the given truth table below, 1 is placed in the parity bit in order to make the total number of bits odd when the total number of 1s in the truth table is even.

|   | 3- <mark>bit messa</mark> | ge | Odd parity bit generator (P) |  |  |  |

|---|---------------------------|----|------------------------------|--|--|--|

| Α | В                         | с  | Y                            |  |  |  |

| 0 | 0                         | 0  | 1                            |  |  |  |

| 0 | 0                         | 1  | 0                            |  |  |  |

| 0 | 1                         | 0  | 0                            |  |  |  |

| 0 | 1                         | 1  | 1                            |  |  |  |

| 1 | 0                         | 0  | 0                            |  |  |  |

| 1 | 0                         | 1  | 1                            |  |  |  |

| 1 | 1                         | 0  | 1                            |  |  |  |

| 1 | 1                         | 1  | 0                            |  |  |  |

#### Table 3. Odd Parity Bit Generator

The truth table of the odd parity generator can be simplified by using K-map as

#### Figure 12. Odd Parity Bit Generator K-Map

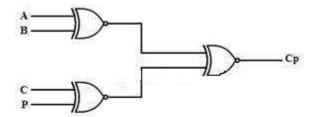

The output parity bit expression for this generator circuit is obtained as  $P = A \bigoplus B \text{ Ex-NOR } C$

The above Boolean expression can be implemented by using one Ex-OR gate and one Ex-NOR gate in order to design a 3-bit odd parity generator. The logic circuit of this generator is shown in below figure , in which . two inputs are applied at one Ex-OR gate, and this Ex-OR output and third input is applied to the Ex-NOR gate , to produce the odd parity bit. It is also possible to design this circuit by using two Ex-OR gates and one NOT gate.

Figure 13. Circuit Diagram of odd parity bit generator

#### **Parity Check**

It is a logic circuit that checks for possible errors in the transmission.

This circuit can be an even parity checker or odd parity checker depending on the type of parity generated at the transmission end. When this circuit is used as even parity checker, the number of input bits must always be even. When a parity **error occurs, the 'sum even' output goes low and 'sum odd' output goes** high. If this logic circuit is used as an odd parity checker, the number of input bits should be odd, but if an erro**r occurs the 'sum odd' output goes low and 'sum even' output goes high.**

#### **Even Parity Checker**

Consider that three input message along with even parity bit is generated at the transmitting end. These 4 bits are applied as input to the parity checker circuit which checks the possibility of error on the data. Since the data is transmitted with even parity, four bits received at circuit must have an even number of 1s.

If any error occurs, the received message consists of odd number of 1s. The output of the parity checker is denoted by PEC (parity error check).

The below table shows the truth table for the even parity checker in which PEC = 1 if the error occurs, i.e., the four bits received have odd number of 1s and PEC = 0 if no error occurs, i.e., if the 4-bit message has even number of 1s.

| 4-  | bit receiv | ed messag | Design and the local sectors |                                   |  |  |  |  |

|-----|------------|-----------|------------------------------|-----------------------------------|--|--|--|--|

| A B |            | C P       |                              | Parity error check C <sub>p</sub> |  |  |  |  |

| 0   | 0          | 0         | 0                            | 0                                 |  |  |  |  |

| 0   | 0          | 0         | 1                            | 1                                 |  |  |  |  |

| 0   | 0          | 1         | 0                            | 1                                 |  |  |  |  |

| 0   | 0          | 1         | 1                            | 0                                 |  |  |  |  |

| 0   | 1          | 0         | 0                            | 1                                 |  |  |  |  |

| 0   | 1          | 0         | 1                            | 0                                 |  |  |  |  |

| 0   | 1          | 1         | 0                            | 0                                 |  |  |  |  |

| 0   | 1          | 1         | 1                            | 1                                 |  |  |  |  |

| 1   | 0          | 0         | 0                            | 1                                 |  |  |  |  |

| 1   | 0          | 0         | 1                            | 0                                 |  |  |  |  |

| 1   | 0          | 1         | 0                            | 0                                 |  |  |  |  |

| 1   | 0          | 1         | 1                            | 1                                 |  |  |  |  |

| 1   | 1          | 0         | 0                            | 0                                 |  |  |  |  |

| 1   | 1          | 0         | 1                            | 1                                 |  |  |  |  |

| 1   | 1          | 1         | 0                            | 1                                 |  |  |  |  |

| 1   | 1          | 1         | 1                            | 0                                 |  |  |  |  |

#### **Table 4. Even Parity Checker**

The above truth table can be simplified using K-map as shown below.

| a        | 00      | 01     | 11              | 10           |

|----------|---------|--------|-----------------|--------------|

| ав<br>00 | 0       |        | 3<br>0          |              |

| 01       |         | 0      |                 | <sup>6</sup> |

| 11       | 12<br>0 | 1      | 0 <sup>15</sup> |              |

| 10       | 1       | 9<br>0 |                 | 10<br>0      |

Figure 14. K-map of even parity checker

$$PEC = \overline{A} \ \overline{B} \ (\overline{C} \ D + \underline{C}, \overline{D}) + \overline{A} \ B \ (\overline{C} \ \overline{D} + C \ D) + A \ B \ (\overline{C} \ D + C \ \overline{D}) + A \ \overline{B} \ (\overline{C} \ \overline{D} + C \ D)$$

$$= \overline{A} \ \overline{B} \ (C \oplus D) + \overline{A} \ B \ (\overline{C} \oplus D) + A \ B \ (C \oplus D) + A \ \overline{B} \ (\overline{C} \oplus D)$$

$$= (\overline{A} \ \overline{B} + A \ B) \ (C \oplus D) + (\overline{A} \ B + \underline{A}, \overline{B}) \ (\overline{C} \oplus D)$$

$$= (A \oplus B) \oplus (C \oplus D)$$

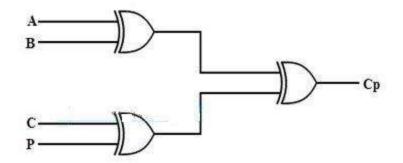

The above logic expression for the even parity checker can be implemented by using three Ex-OR gates as shown in figure. If the received message consists of five bits, then one more Ex-OR gate is required for the even parity checking.

Figure 15. Logic Diagram of even parity checker

#### **Odd Parity Checker**

Consider that a three bit message along with odd parity bit is transmitted at the transmitting end. Odd parity checker circuit receives these 4 bits and checks whether any error are present in the data. If the total number of 1s in the data is odd, then it indicates no error, whereas if the total number of 1s is even then it indicates the error since the data is transmitted with odd parity at transmitting end.

The below figure shows the truth table for odd parity generator where **PEC** =1 if the 4-bit message received consists of even number of 1s (hence the error occurred) and **PEC**= 0 if the message contains odd number of 1s (that means no error).

| 4- | bit receive | ed messag | Devites annual basis C |                       |  |  |  |

|----|-------------|-----------|------------------------|-----------------------|--|--|--|

| A  | B           | C         | Р                      | Parity error check Cp |  |  |  |

| 0  | 0           | 0         | 0                      | 1                     |  |  |  |

| 0  | 0           | 0         | 1                      | 0                     |  |  |  |

| 0  | 0           | 1         | 0                      | 0                     |  |  |  |

| 0  | 0           | 1         | 1                      | 1                     |  |  |  |

| 0  | 1           | 0         | 0                      | 0                     |  |  |  |

| 0  | 1           | 0         | 1                      | 1                     |  |  |  |

| 0  | 1           | 1         | 0                      | 1                     |  |  |  |

| 0  | 1           | 1         | 1                      | 0                     |  |  |  |

| 1  | 0           | 0         | 0                      | 0                     |  |  |  |

| 1  | 0           | 0         | 1                      | 1                     |  |  |  |

| 1  | 0           | 1         | 0                      | 1                     |  |  |  |

| 1  | 0           | 1         | 1                      | 0                     |  |  |  |

| 1  | 1           | 0         | 0                      | 1                     |  |  |  |

| 1  | 1           | 0         | 1                      | 0                     |  |  |  |

| 1  | 1           | 1         | 0                      | 0                     |  |  |  |

| 1  | 1           | 1         | 1                      | 1                     |  |  |  |

#### Table 5. Odd Parity Checker

The expression for the PEC in the above truth table can be simplified by K-map as shown below.

Figure 16. K-map of odd parity checker

After simplification, the final expression for the PEC is obtained as

PEC = (A Ex-NOR B) Ex-NOR (C Ex-NOR D)

The expression for the odd parity checker can be designed by using three Ex-NOR gates as shown below.

Figure 17. Logic Diagram of odd parity checker

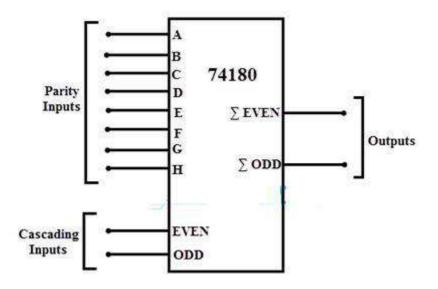

#### **Parity Generator/Checker ICs**

There are different types of parity generator /checker ICs are available with different input configurationssuch as 5-bit, 4-bit, 9-bit, 12-bit, etc.

A most commonly used and standard type of parity generator/checker IC is 74180.It is a 9-bit parity generator or checker used to detect errors in high speed data transmission or data retrieval systems. The figure below shows the pin diagram of 74180 IC.This IC can be used to generate a 9-bit odd or even parity code or it can be used to check for odd or even parity in a 9-bit code (8 data bits and one parity bit).

Figure 18. Graphic Diagram of Parity Generator

This IC consists of eight parity inputs from A through H and two cascading inputs. There are two outputs even sum and odd sum. In implementing generator or checker circuits, unused parity bits must be tied to logic zero and the cascading inputs must not be equal.

# Lecture 7 & Lecture 8

# Encoder, Decoder, Multiplexer

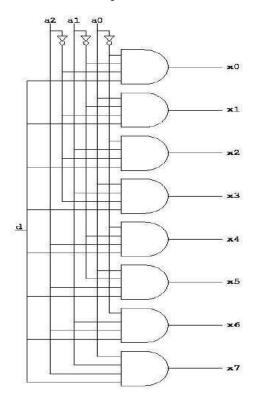

# Encoder

An encoder has  $2^{n}$  input lines and *n* output lines. The output lines generate a binary code corresponding to the input value. For example a single bit 4 to 2 encoder takes in 4 bits and outputs 2 bits. It is assumed that there are only 4 types of input signals these are : 0001, 0010, 0100, 1000.

| I3 | $\mathbf{I}_2$ | $\mathbf{I}_1$ | Io | Fı | Fo |

|----|----------------|----------------|----|----|----|

| 0  | 0              | 0              | 1  | 0  | 0  |

| 0  | 0              | 1              | 0  | 0  | 1  |

| 0  | 1              | 0              | 0  | 1  | 0  |

| 1  | 0              | 0              | 0  | 1  | 1  |

(a)Truth Table of 4 to 2 encoder

(b) Circuit Diagram of encoder

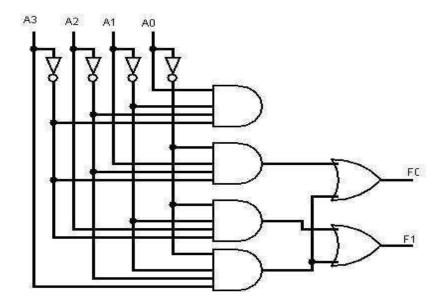

#### Figure 19. (a) Truth Tablee and (b) Circuit Diagram of Encoder

The encoder has the limitation that only one input can be active at any given time. If two inputs are simultaneously active, the output produces an undefined combination. To prevent this we make use of

the priority encoder.

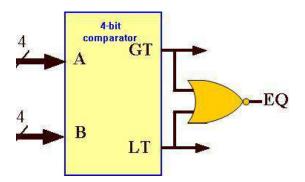

# Decoder

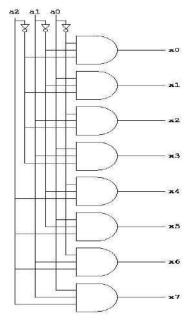

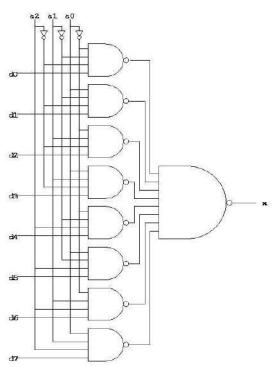

In both the multiplexer and the demultiplexer, part of the circuits *decode* the address inputs, i.e. it translates a binary number of n digits to  $2^{n}$  outputs, one of which (the one that corresponds to the value of the binary number) is 1 and the others of which are 0.

It is sometimes advantageous to separate this function from the rest of the circuit, since it is useful in many other applications. Thus, we obtain a new combinatorial circuit that we call the *decoder*. It has the following truth table (for n = 3):

a2 a1 a0 | x7 x6 x5 x4 x3 x2 x1 x0

| 0 | 0 | 0 0 0 0 0 0 0 0 0 1 |

|---|---|---------------------|

| 0 | 0 | 1   0 0 0 0 0 0 1 0 |

| 0 | 1 | 0 0 0 0 0 0 1 0 0   |

| 0 | 1 | 1   0 0 0 0 1 0 0 0 |

| 1 | 0 | 0 0 0 0 1 0 0 0 0   |

| 1 | 0 | 1   0 0 1 0 0 0 0 0 |

| 1 | 1 | 0 0 1 0 0 0 0 0 0   |

| 1 | 1 | 1   1 0 0 0 0 0 0 0 |

(a) Truth Table of decoder

(b) circuit diagram for the decoder

#### Figure 20. (a) Truth Table and (b) Circuit Diagram of Decoder

# Multiplexer

SELECT

A multiplexer is a combinatorial circuit that is given a certain number (usually a power of two) *data inputs*, let us say  $2^n$ , and n *address inputs* used as a binary number to select one of the data inputs. The multiplexer has a single output, which has the same value as the selected data input.

In other words, the multiplexer works like the input selector of a home music system. Only one input is selected at a time, and the selected input is transmitted to the single output. While on the music system, the selection of the input is made manually, the multiplexer chooses its input based on a binary number, the address input.

The truth table for a multiplexer is huge for all but the smallest values of n. We therefore use an abbreviated version of the truth table in which some inputs are replaced by `-' to indicate that the input value does not matter.

Here is such an abbreviated truth table for n = 3. The full truth table would have  $2^{(3+23)} = 2048$  rows.

| <u>SELECT</u> |    |     |    |    | INPUT |    |    |    |    |     |       |

|---------------|----|-----|----|----|-------|----|----|----|----|-----|-------|

| a2            | a1 | a() | d7 | d6 | d5    | d4 | d3 | d2 | d1 | d() | )   x |

| -             | -  | -   | -  | -  | -     | -  | -  | -  | -  | -   |       |

| 0             | 0  | 0   | -  | -  | -     | -  | -  | -  | -  | 0   | 0     |

| 0             | 0  | 0   | -  | -  | -     | -  | -  | -  | -  | 1   | 1     |

| 0             | 0  | 1   | -  | -  | -     | -  | -  | -  | 0  | -   | 0     |

| 0             | 0  | 1   | -  | -  | -     | -  | -  | -  | 1  | -   | 1     |

| 0             | 1  | 0   | -  | -  | -     | -  | -  | 0  | -  | -   | 0     |

| 0             | 1  | 0   | -  | -  | -     | -  | -  | 1  | -  | -   | 1     |

| 0             | 1  | 1   | -  | -  | -     | -  | 0  | -  | -  | -   | 0     |

| 0             | 1  | 1   | -  | -  | -     | -  | 1  | -  | -  | -   | 1     |

| 1             | 0  | 0   | -  | -  | -     | 0  | -  | -  | -  | -   | 0     |

| 1             | 0  | 0   | -  | -  | -     | 1  | -  | -  | -  | -   | 1     |

| 1             | 0  | 1   | -  | -  | 0     | -  | -  | -  | -  | -   | 0     |

| 1             | 0  | 1   | -  | -  | 1     | -  | -  | -  | -  | -   | 1     |

| 1             | 1  | 0   | -  | 0  | -     | -  | -  | -  | -  | -   | 0     |

| 1             | 1  | 0   | -  | 1  | -     | -  | -  | -  | -  | -   | 1     |

| 1             | 1  | 1   | 0  | -  | -     | -  | -  | -  | -  | -   | 0     |

| 1             | 1  | 1   | 1  | -  | -     | -  | -  | -  | -  | -   | 1     |

INDUT

(a) Truth Table of multiplexer

We can abbreviate this table even more by using a letter to indicate the value of the selected input, like

this:

a2 a1 a0 d7 d6 d5 d4 d3 d2 d1 d0 | Х --- -000 с С 001 с С 010 с С 011 с с  $1 \ 0 \ 0$ с С 101 С -С 110 С С 111 с С

(b) Truth Table of multiplexer

The same way we can simplify the truth table for the multiplexer, we can also simplify the corresponding circuit. Indeed, our simple design method would yield a very large circuit. The simplified circuit looks like this:

(c) Circuit Diagram of multiplexer

#### Figure 21. Truth Table and Circuit Diagram of Multiplexer

# Lecture 9

# **De-Multiplexer**, Comparator[[1L]

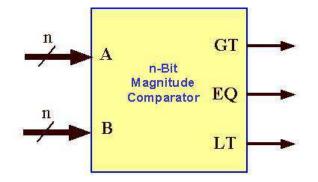

### **Magnitude Comparator**

A magnitude comparator is a combinational circuit that compares two numbers A & B to determine whether:

$$A > B$$

, or  $A = B$ , or  $A < B$

Inputs :

First *n*-bit number A

Second *n*-bit number B

Outputs :

3 output signals (GT, EQ, LT), where:

3. GT = 1 IFF A > B 4. EQ = 1 IFF A = B LT = 1 IFF A < B

It must be noted Exactly One of these 3 outputs equals 1, while the other 2 outputs are 0's.

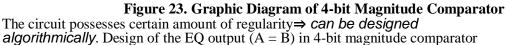

Figure 22. Graphic Diagram of n-bit Magnitude Comparator

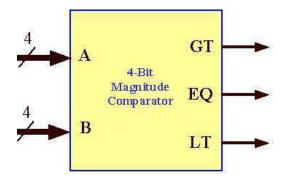

4-bit magnitude ⇒comparator⇒ Inputs: 8-bits (A 4-bits , B 4-bits)

A and B are two 4-bit numbers

#### Let A = A3A2A1A0, and

#### Let B = B3B2B1B0

Inputs have 28 (256) possible combinations

Not easy to design using conventional technique.

Define Xi = (Ai Bi) + (Ai

/ Bi

/)

Thus Xi = 1 IFF Ai = Bi i = 0, 1, 2 and 3

Xi = 0 IFF  $Ai \neq Bi$   $\forall$

Condition for A= B

*EQ*=1 (i.e., *A*=*B*) IFF

7. A3=B3  $\rightarrow$  (X3 = 1), and

8. A2=B2  $\rightarrow$  (X2 = 1), and

9. A1=B1  $\rightarrow$  (X1 = 1), and

10.

$$A0=B0 \rightarrow (X0 = 1).$$

Thus, EQ=1 IFF X3 X2 X1 X0 = 1. In other words, EQ = X3 X2 X1 X0

### Design of the GT output (A >B) 4-bit magnitude comparator

If A3 > B3, then A > B (GT=1) irrespective of the relative values of the other bits of A &B. Consider, for example, A = 1000 and B = 0111 where A > B.This can be stated as GT=1 if A3 B3/=1

If A3 = B3 (X3 = 1), we compare the next significant pair of bits (A2 & B2).

If A2 > B2 then A > B (GT=1) irrespective of the relative values of the other bits of A &B. Consider, for example, A = 0100 and B = 0011 where A > B. This can be stated as GT=1 if **X3A2 B2/ =1**

If A3 = B3 (X3 = 1) and A2 = B2 (X2 = 1), we compare the next significant pair of bits (A1& B1).

If A1 > B1 then A > B (GT=1) irrespective of the relative values of the remaining bits A0& B0. Consider, for example, A = 0010 and B = 0001 where A > B. This can be stated as GT=1 if **X3 X2A1 B1/=1**

If A3 = B3 (X3 = 1) and A2 = B2 (X2 = 1) and A1 = B1 (X1 = 1), we compare the next pairof bits (A0 &B0).

If A0 > B0 then A > B (GT=1). This can be stated as GT=1 if **X3X2X1A0B0/=1**

To summarize, GT = 1 (A > B) IFF:

- = A3 B3/=1, or

- = X3A2 B2/=1, or

- = **X3 X2A1 B1/ = 1**, or

- = X3X2X1A0B0/=1

In other words, GT = A3 B3/ + X3A2 B2/ + X3 X2A1 B1/ + X3X2X1A0B0/

#### **Design of the LT output (A <B) 4-bit magnitude comparator**

In the same manner as above, we can derive the expression of the LT (A <B) output

#### LT = B3 A3 / + X3B2 A2 / + X3 X2B1 A1 / + X3X2X1B0A0 /

The gate implementation of the three output variables (EQ, GT & LT) is shown in the figure below.

Figure 24. Circuit Diagram of Comparator

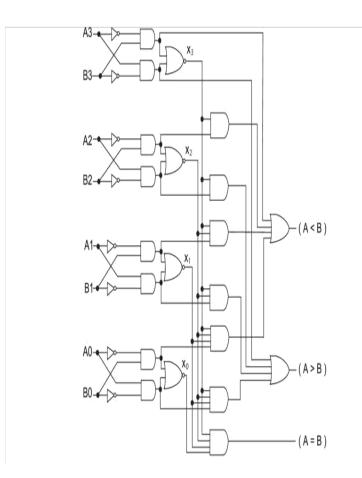

### Modification to the Design

The hardware in the comparator can be reduced by implementing only two outputs, andthe third output can be obtained using these two outputs.For example, if we have the LT and GT outputs, then the EQ output can be obtained by using only a NOR gate, as shown in the figure below.

Figure 25. Graphic Diagram of modified 4-bit Magnitude Comparator

Thus, when both the GT and LT outputs are zeros, then the 3rd one (i.e. EQ) is a '1'.

# Demultiplexer

The de-multiplexer is the inverse of the multiplexer, in that it takes a single data input and n address inputs. It has  $2^n$  outputs. The address input determine which data output is going to have the same value as the data input. The other data outputs will have the value 0. Here is an abbreviated truth table for the de-multiplexer. We could have given the full table since it has only 16 rows, but we will use the same convention as for the multiplexer where we abbreviated the values of the data inputs.

a2 a1 a0 d | x7 x6 x5 x4 x3 x2 x1 x0

(a) Truth table for the demultiplexer

(b) circuit diagram for the demultiplexer

# Lecture 10 Basic Concepts of A/D and D/A converters[1L]

### Analog to Digital Converters (A/D)

An electronic integrated circuit which transforms a signal from analog (continuous)to digital (discrete) form. Analog signals are directly measurable quantities. Digital signals only have two states. For digital computer, we refer to binary states, 0 and 1.

#### **Need For A/D Converter**

Microprocessors can only perform complex processing on digitized signals. When signals are in digital form they are less susceptible to the deleterious effects of additive noise.ADC Provides a link between the analog world of transducers and the digital world of signal processing and data handling.

### **Application Of A/D Converter**

ADC are used virtually everywhere where analog signal has to be processed, stored, or transported in digital form. Some examples of ADC usage are digital voltmeters, cell phone, thermocouples, an digital oscilloscope. Microcontrollers commonly use 8, 10, 12, or16 bit ADCs, our micro controller uses an 8 or10 bit ADC.

### The ADC Process

ADC is a two step process: Sampling and Holding (S/H) and Quantizing and Encoding (Q/E).

### Sampling and Holding (S/H)

Holding signal benefits the accuracy of the A/D conversion.Minimum sampling rate should be at least twice the highest data frequency of the analog signal.

# Quantizing and Encoding (Q/E)

Resolution:

The smallest change in analog signal that will result in a change in the digital output.

V = Reference voltage range

N = Number of bits in digital output.

2N = Number of states.

### $\Delta V = Resolution$

The resolution represents the quantization error inherent in the conversion of the signal to digital form.

Quantizing: Partitioning the reference signal range into a number of discrete quanta, then matching the input signal to the correct quantum.

Encoding: Assigning a unique digital code to each quantum, then allocating the digital code to the input signal.

# **Types of A/D Converters**

- 1) Dual Slope A/D Converter

- 2) Successive Approximation A/D Converter

- 3) Flash A/D Converter

- 4) Delta-Sigma A/D Converter

Other, Voltage-to-frequency, staircase ramp or single slope, charge balancing or redistribution, switched capacitor, tracking, and resolver.

# **ADC Types Comparison**

| Туре             | Speed (relative) | Cost (relative) |

|------------------|------------------|-----------------|

| Dual slope       | Slow             | Med             |

| Flash            | Very fast        | High            |

| Successive Appox | Medium – Fast    | Low             |

| Sigma-Delta      | Slow             | Low             |

Table 1. ADC Type Comparison Table

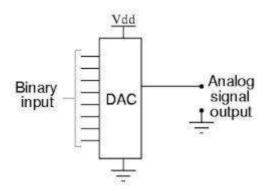

# Digital to Analog Converters (D/A)

The process of converting digital signal into equivalent analog signal is called D/A conversion. The electronics circuit, which does this process, is called D/A converter. **The circuit has 'n' number of** digital data inputs with only one output. Basically, there are two types of D/A converter circuits: Weighted resistors D/A converter circuit and Binary ladder or R–2R ladder D/A converter circuit.

Weighted resistors D/A converter – here an opamp is used as summing amplifier. There are four resistors R, 2R, 4R and 8R at the input terminals of the opamp with R as feedback resistor. The network of resistors at the input terminal of opamp is called as variable resistor network. The four inputs of the circuit are D, C, B & A. Input D is at MSB and A is at LSB. Here we shall connect 8V DC voltage as logic–1 level. So we shall assume that 0 = 0V and 1 = 8V. Now the working of the circuit is as follows.

Figure 1.Graphic Diagram of D/A Converter

### **Application Of D/A Converter**

Audio : DACs are commonly used in music players to convert digital data streams into analog audio signals.

**Video** : They are also used in televisions and mobile phones to convert digital video data into analog video signals which connect to the screen drivers to display monochrome or color images.

These two applications use DACs at opposite ends of the speed/resolution trade-off. The audio DAC is a low speed high resolution type while the video DAC is a high speed low to medium resolution type.

Discrete DACs would typically be extremely high speed low resolution power hungry types, as used in military radar systems. Very high speed test equipment, especially sampling oscilloscopes, may also use discrete DACs.

### **Types Of D/A Converter**

The most common types of electronic DACs are:

1) The **pulse-width modulator**, the simplest DAC type.

- 2) The **delta-sigma DAC**.

- 3) The **R-2R ladder** DAC.

- 4) The Successive-Approximation or Cyclic DAC.

- 5) The thermometer-coded DAC.

# Lecture 11,12 &13

### **Basic Flip-flop- SR, JK, D, T and JK Master-slave Flip Flops**

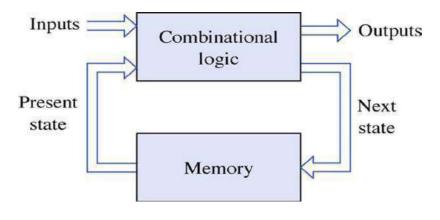

# **Sequential circuit**

### Introduction

In order to build sophisticated digital logic circuits, including computers, we need more a powerful model. We need circuits whose output depends upon both the input of the circuit and its previous state. In other words, we need circuits that have *memory*.

For a device to serve as a memory, it must have three characteristics:

- 5. the device must have two stable states

- 6. there must be a way to read the state of the device

- 7. there must be a way to set the state at least once.

It is possible to produce circuits with memory using the digital logic gates we've already seen. To do that, we need to introduce the concept of *feedback*. So far, the logical flow in the circuits we've studied has been from input to output. Such a circuit is called *acyclic*. Now we will introduce a circuit in which the output is fed back to the input, giving the circuit memory. (There are other memory technologies that store electric charges or magnetic fields; these do not depend on feedback.)

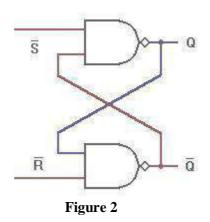

Figure 1

### Latches and flip-flops

In the same way that gates are the building blocks of combinatorial circuits, latches and

*flip-flops* are the building blocks of sequential circuits.

While gates had to be built directly from transistors, latches can be built from gates, and flip-flops can be built from latches. This fact will make it somewhat easier to understand latches and flip-flops.

Both latches and flip-flops are circuit elements whose output depends not only on the current inputs, but also on previous inputs and outputs. The difference between a latch and a flip-flop is that a latch does not have a *clock signal*, whereas a flip-flop always does.

### Latches

How can we make a circuit out of gates that is not combinatorial? The answer is *feed-back*, which means that we create *loops* in the circuit diagrams so that output values depend, indirectly, on themselves. If such feed-back is *positive* then the circuit tends to have stable states, and if it is *negative* the circuit will tend to oscillate.

In order for a logical circuit to "remember" and retain its logical state even after the controlling input signal(s) have been removed, it is necessary for the circuit to include some form of feedback. We might start with a pair of inverters, each having its input connected to the other's output. The two outputs will always have opposite logic level.

The problem with this is that we don't have any additional inputs that we can use to change the logic states if we want. We can solve this problem by replacing the inverters with NAND or NOR gates, and using the extra input lines to control the circuit.

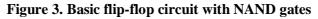

The circuit shown below is a basic NAND latch. The inputs are generally designated "S" and "R" for "Set" and "Reset" respectively. Because the NAND inputs must normally be logic 1 to avoid affecting the latching action, the inputs are considered to be inverted in this circuit.

The outputs of any single-bit latch or memory are traditionally designated Q and Q'. In a commercial latch circuit, either or both of these may be available for use by other circuits. In any case, the circuit itself is:

For the NAND latch circuit, both inputs should normally be at a logic 1 level. Changing an input to a logic 0 level will force that output to a logic 1. The same logic 1 will also be

applied to the second input of the other NAND gate, allowing that output to fall to a logic 0 level. This in turn feeds back to the second input of the original gate, forcing its output to remain at logic 1.

Applying another logic 0 input to the same gate will have no further effect on this circuit. However, applying a logic 0 to the *other* gate will cause the same reaction in the other direction, thus changing the state of the latch circuit the other way.

Note that it is forbidden to have both inputs at a logic 0 level at the same time. That state will force both outputs to a logic 1, overriding the feedback latching action. In this condition, whichever input goes to logic 1 first will lose control, while the other input (still at logic 0) controls the resulting state of the latch. If both inputs go to logic 1 simultaneously, the result is a "race" condition, and the final state of the latch cannot be determined ahead of time. The same functions can also be performed using NOR gates. A few adjustments must be made to allow for the difference in the logic function, but the logic involved is quite similar.

The circuit shown below is a basic NOR latch. The inputs are generally designated "S" and "R" for "Set" and "Reset" respectively. Because the NOR inputs must normally be logic 0 to avoid overriding the latching action, the inputs are not inverted in this circuit. The NOR-based latch circuit is:

For the NOR latch circuit, both inputs should normally be at a logic 0 level. Changing an input to a logic 1 level will force that output to a logic 0. The same logic 0 will also be applied to the second input of the other NOR gate, allowing that output to rise to a logic 1 level. This in turn feeds back to the second input of the original gate, forcing its output to remain at logic 0 even after the external input is removed.

Applying another logic 1 input to the same gate will have no further effect on this circuit. However, applying a logic 1 to the *other* gate will cause the same reaction in the other direction, thus changing the state of the latch circuit the other way.

Note that it is forbidden to have both inputs at a logic 1 level at the same time. That state will force both outputs to a logic 0, overriding the feedback latching action. In this condition, whichever input goes to logic 0 first will losecontrol, while the other input (still at logic 1) controls the resulting state of the latch. If both inputs go to logic 0simultaneously, the result is a "race" condition, and the final state of the latch cannot be determined ahead of time.

One problem with the basic RS NOR latch is that the input signals actively drive their respective outputs to a logic 0, rather than to a logic 1. Thus, the S input signal is applied to the gate that produces the Q' output, while the R input signal is applied to the gate that produces the Q output. The circuit works fine, but this reversal of inputs can be confusing when you first try to deal with NOR-based circuits.

### **Flip-flops**

Latches are asynchronous, which means that the output changes very soon after the input changes. Most computers today, on the other hand, are synchronous, which means that the outputs of all the sequential circuits change simultaneously to the rhythm of a global clock signal.

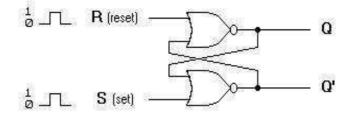

A flip-flop is a synchronous version of the latch. A flip-flop circuit can be constructed from two NAND gates or two NOR gates. These flip-flops are shown in Figure 2 and Figure 3. Each flip-flop has two outputs, Q and Q', and two inputs, set and reset. This type of flip-flop is referred to as an SR flip-flop or SR latch. The flip-flop in Figure 2 has two useful states. When Q=1 and Q'=0, it is in the set state

(or 1-state). When Q=0 and Q'=1, it is in the clear state (or 0 -state). The outputs Q and Q' are complements of each other and are referred to as the normal and complement outputs, respectively. The binary state of the flip-flop is taken to be the value of the normal output.

When a 1 is applied to both the set and reset inputs of the flip-flop in Figure 2, both Q and  $\mathbf{Q'}$  outputs go to 0. This condition violates the fact that both outputs are complements of each other. In normal operation this condition must be avoided by making sure that 1's are not applied to both inputs simultaneously.

(a) Logic diagram

| SR | Q Q' |                              |

|----|------|------------------------------|

| 10 | 10   | •25                          |

| 00 | 10   | (after S=1, R=0)             |

| 01 | 01   | 1630/PORTAXENIN: PERIOD 2047 |

| 00 | 01   | (after S=0, R=1)             |

| 11 | 00   | 97 32 98                     |

(b) Truth table

Figure 4. Basic flip-flop circuit with NAND gates

The NAND basic flip-flop circuit in Figure 3(a) operates with inputs normally at 1 unless the state of the flip-flop has to be changed. A 0 applied momentarily to the set input causes Q to go to 1 and Q' to go to 0, putting the flip-flop in the set state. When both inputs go to 0, both outputs go to 1. This condition should be avoided in normal operation.

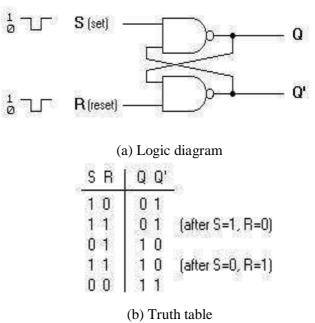

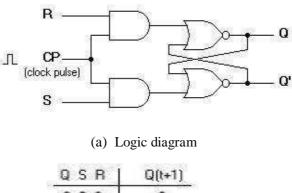

#### **Clocked SR Flip-Flop**

The clocked SR flip-flop shown in Figure 4 consists of a basic NOR flip-flop and two AND gates. The outputs of the two AND gates remain at 0 as long as the clock pulse (or CP) is 0, regardless of the S and R input values. When the clock pulse goes to 1, information from the S and R inputs passes through to the basic flip-flop. With both S=1 and R=1, the occurrence of a clock pulse causes both outputs to momentarily go to 0. When the pulse is removed, the state of the flip-flop is indeterminate, i.e., either state may result, depending on whether the set or reset input of the flip-flop remains a 1 longer than the transition to 0 at the end of the pulse.

| QSR | Q(t+1)        |

|-----|---------------|

| 000 | 0             |

| 001 | 0             |

| 010 | 1             |

| 011 | indeterminate |

| 100 | 1             |

| 101 | 0             |

| 110 | 1             |

| 111 | indeterminate |

|     |               |

(b) Truth Table

Figure 5. Clocked S R Flip Flop

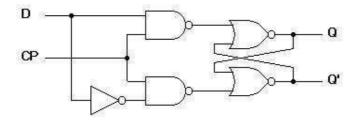

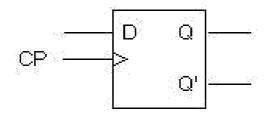

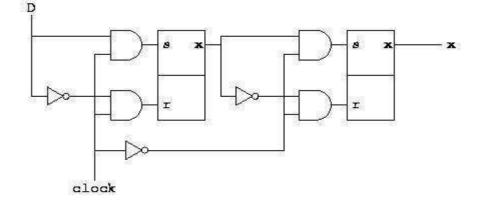

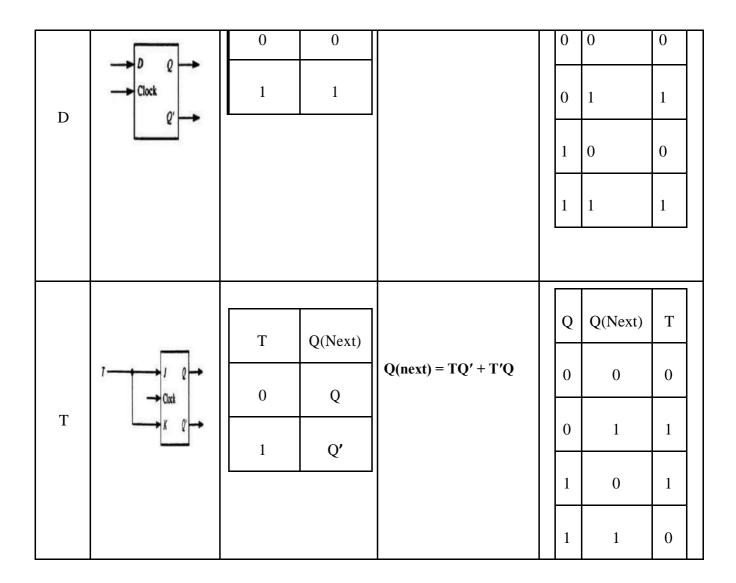

#### **D** Flip-Flop

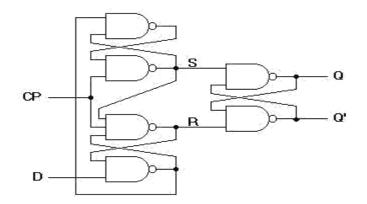

The D flip-flop shown in Figure 5 is a modification of the clocked SR flip-flop. The D input goes directly into the S input and the complement of the D input goes to the R input. The D input is sampled during the occurrence of a clock pulse. If it is 1, the flip-flop is switched to the set state (unless it was already set). If it is 0, the flip-flop switches to the clear state.

(a) Logic diagram with NAND gates

(b) Graphical symbol

| Q(t+1) |

|--------|

| 0      |

| 1      |

| 0      |

| 1      |

|        |

(c) Transition table

Figure 6. Clocked D flip-flop

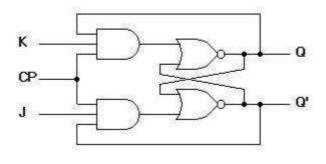

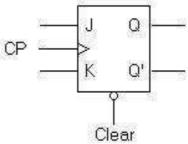

#### **JK Flip-Flop**

A JK flip-flop is a refinement of the SR flip-flop in that the indeterminate state of the SR type is defined in the JK type. Inputs J and K behave like inputs S and R to set and clear the flip-flop (note that in a JK flip-flop, the letter J is for set and the letter K is for clear). When logic 1 inputs are applied to both J and K simultaneously, the flip-flop switches to its complement state, ie., if Q=1, it switches to Q=0 and vice versa.

A clocked JK flip-flop is shown in figure below. Output Q is ANDed with K and CP inputs so that the flip-flop is cleared during a clock pulse only if Q was previously 1. Similarly, ouput Q' is ANDed with J and CP inputs so that the flip-flop is set with a clock pulse only if Q' was previously 1.

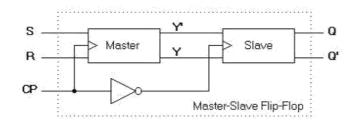

Note that because of the feedback connection in the JK flip-flop, a CP signal which remains a 1 (while J=K=1) after the outputs have been complemented once will cause repeated and continuous transitions of the outputs. To avoid this, the clock pulses must have a time duration less than the propagation delay through the flip-flop. The restriction on the pulse width can be eliminated with a master-slave or edge-triggered construction. The same reasoning also applies to the T flip-flop presented next.

(a) Logic diagram

| Q  | JI | < 1 | Q(t+1) |

|----|----|-----|--------|

| 0  | 0  | 0   | 0      |

| 0  | 0  | 1   | 0      |

| 0  | 1  | 0   | 1      |

| 0  | 1  | 1   | ্র     |

| 1  | 0  | 0   | 3      |

| 1  | 0  | 1   | 0      |

| 1  | 1  | 0   | 1      |

| Э. | 1  | 1   | 0      |

(b) Transition Table

### Figure 7. Clocked JK flip-flop

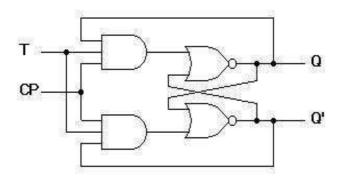

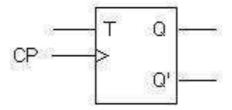

# T Flip-Flop

The T flip-flop is a single input version of the JK flip-flop. As shown in figure below, the T flip-flop is obtained from the JK type if both inputs are tied together. The output of the T flip-flop "toggles" with each clock pulse.

(a) Logic diagram

(b) Graphical symbol

| QT | Q(t+1) |

|----|--------|

| 00 | 0      |

| 01 | 1      |

| 10 | 1      |

| 11 | 0      |

(c) Transition table

Figure 8. T Flip Flop

### **Triggering of Flip-flops**

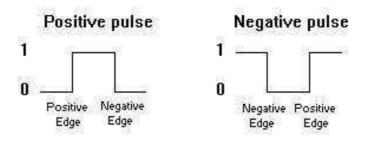

The state of a flip-flop is changed by a momentary change in the input signal. This change is called a trigger and the transition it causes is said to trigger the flip-flop. The basic circuits of Figure 2 and Figure 3 require an input trigger defined by a change in signal level. This level must be returned to its initial level before a second trigger is applied. Clocked flip-flops are triggered by pulses.

The feedback path between the combinational circuit and memory elements in Figure 1 can produce instability if the outputs of the memory elements (flip-flops) are changing while the outputs of the combinational circuit that go to the flip-flop inputs are being sampled by the clock pulse. A way to solve the feedback timing problem is to make the flip-flop sensitive to the pulse transition rather than the pulse duration.

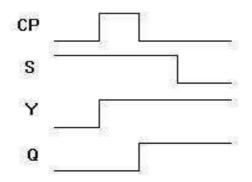

The clock pulse goes through two signal transitions: from 0 to 1 and the return from 1 to 0. As shown in Figure, the positive transition is defined as the positive edge and the negative transition as the negative edge.

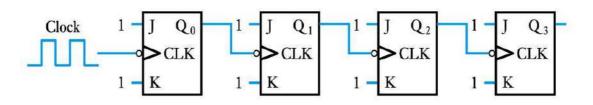

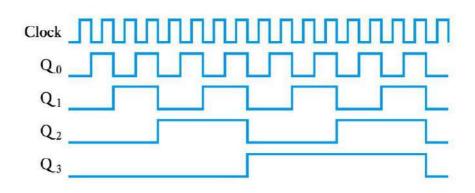

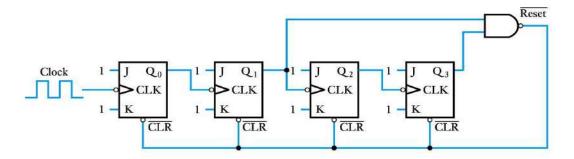

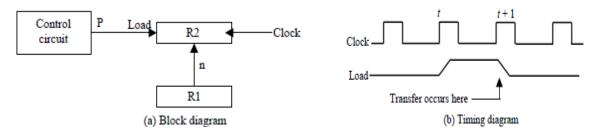

Figure 9 . Definition of clock pulse transition