Name of the Paper: Microprocessors & Microcontrollers Paper Code: CS602 Contact (Periods/Week): 3L/Week Credit Point: 3 No. of Lectures: 35

## **Prerequisite:**

- 1. Familiarity with the number system

- 2. A solid background in digital logic.

## **Course Objective(s)**

- To learn the basics of a particular microprocessor.

- To learn the basics of a particular microcontroller.

- To learn the interfacing of microprocessor.

## **Course Outcomes**

**CS602.1** To acquire the knowledge of hardware details of 8085 and 8086 microprocessor with the related signals and their implications

CS602.2 To develop skill in assembly Language programming of 8085

**CS602.3** To understand the concept and techniques of designing and implementing interfacing of microprocessor with memory and peripheral chips involving system design

CS602.4 To acquire the knowledge of the 8051 architecture and its programming

CS602.5 To analyze the performance of computers and its architecture to real-life applications

## Module -1: [9L]

Introduction to Microcomputer based system. [1L]

History of evolution of Microprocessor and Microcontrollers and their advantages and disadvantages. [1L]

Architecture of 8085 Microprocessor, Pin description of 8085. [2L] Address/data bus Demultiplexing, Status Signals and the control signals. [1L]

Interrupts of 8085 processor (software and hardware) [2L]

```

I/O Device Interfacing - I/O Mapped I/O and Memory Mapped I/O,

Memory interfacing with 8085 [2L]

```

## Module -2: [11L]

Instruction set of 8085 microprocessor, Addressing modes. [3L] Assembly language programming with examples, Counter and Time Delays, Stack and Subroutine. [6L] Timing diagram of the instructions (a few examples) [2L] **Module 3: [8L]**

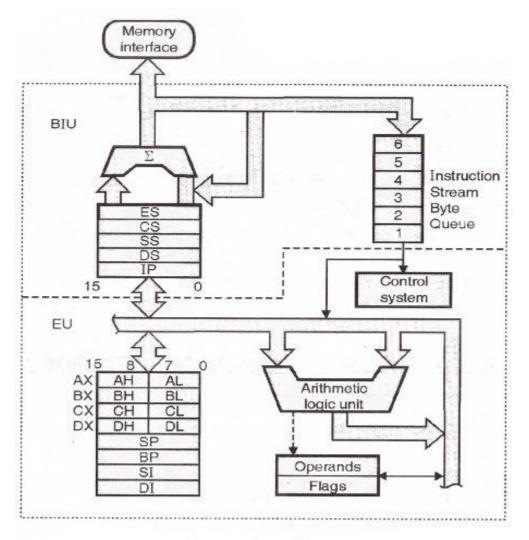

## Online Courseware for B.Tech. Computer Science and Engineering Program (Autonomy) Paper Name: Microprocessor and Microcontrollers Paper Code: CS602 The 8086 microprocessor- Architecture, Pin Details, Addressing modes, Interrupts [3L]

Instruction set, Examples of Simple Assembly Language [3L] Memory interfacing with 8086 [2L]

## Module -4: [7L]

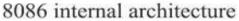

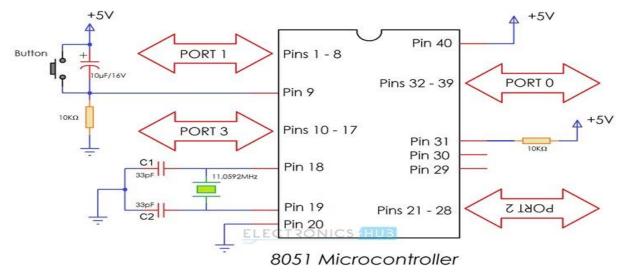

Introduction to 8051 Microcontroller – Architecture, Pin Details. [3L] Addressing modes, Instruction set, Examples of Simple Assembly Language. [4L]

## **Text Books:**

- 1. MICROPROCESSOR architecture, programming and Application with 8085 R. Gaonkar (Penram international Publishing LTD.) [For Module 1 and 2]

- 2. Fundamentals of Microprocessor and Microcontrollers B. Ram (Paperback) [For Module 3]

- 3. 8051 Microcontroller K. Ayala (Cengage learning) [For Module 4]

## **Recommended books:**

- 1. 8086 Microprocessor K Ayala (Cengage learning)

- 2. The 8051 microcontroller and Embedded systems Mazidi, Mazidi and McKinley (PEARSON)

- 3. Microprocessors The 8086/8088, 80186/80386/80486 and the Pentium family N. B. Bahadure (PHI).

| CO      | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| CS602.1 | 3   |     | 3   |     |     |     |     |     |     |      | 2    |      |

| CS602.2 |     |     | 2   | 1   |     |     |     |     |     |      |      |      |

| CS602.3 | 1   |     | 3   | 2   |     | 1   | 1   |     |     |      | 1    |      |

| CS602.4 | 2   |     | 1   |     |     |     |     |     |     |      |      |      |

| CS602.5 |     |     |     | 2   |     | 2   | 2   |     |     |      | 2    |      |

#### **CO-PO Mapping**

## COMPARISON STUDY

| Мо  | No. of | Existing Syllabus as per                                                                                                                                                                                                                                                                                                                                                                                                                                                | Addition/Deletion/ Comment                                                                                                                                                                                                                                                                                                                                                                                                                          | Justification                                                                                   | Syllabus for Autonomy                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| dul | Lectu  | MAKAUT(Module basis)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                     | • • • • • • • • • • • • • • • • • • • •                                                         | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| е   | res    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1   | 9      | Module -1: [8L]<br>Introduction to Microcomputer based<br>system. History of evolution of<br>Microprocessor and Microcontrollers<br>and their advantages and<br>disadvantages. [1L]<br>Architecture of 8085 Microprocessor,<br>Pin description of 8085. [2L]<br>Address/data bus De-multiplexing ,<br>Status Signals and the control signals.<br>[1L]<br>Instruction set of 8085 microprocessor,<br>Addressing modes, [3L]<br>Timing diagram of the instructions (a few | Instruction set of 8085<br>microprocessor, Addressing<br>modes and Timing diagram of<br>the instructions (a few<br>examples) has been shifted to<br>Module 2.<br>Interrupts of 8085 processor<br>(software and hardware), I/O<br>Device Interfacing-I/O Mapped<br>I/O and Memory Mapped I/O<br>has been placed in Module 1.<br>Memory interfacing with 8085                                                                                         | 8085<br>Hardware<br>model and<br>software<br>model has<br>been placed<br>in separate<br>modules | Module -1: [9L]<br>Introduction to Microcomputer based<br>system. [1L]<br>History of evolution of Microprocessor and<br>Microcontrollers and their advantages and<br>disadvantages. [1L]<br>Architecture of 8085 Microprocessor, Pin<br>description of 8085. [2L] Address/data bus<br>De-multiplexing, Status Signals and the<br>control signals. [1L]<br>Interrupts of 8085 processor (software and<br>hardware) [2L]<br>I/O Device Interfacing - I/O Mapped I/O and<br>Memory Mapped I/O, |

|     |        | examples). [1L]                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                 | Memory interfacing with 8085 [2L]                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2   | 11     | Module -2: [9L]<br>Assembly language programming with<br>examples, Counter and Time Delays,<br>Stack and Subroutine, [6L]<br>Interrupts of 8085 processor (software and<br>hardware), I/O Device Interfacing-I/O<br>Mapped I/O and Memory Mapped I/O ,<br>Serial (using SID and SOD pins and RIM,<br>SIM Instructions) and Parallel data<br>transfer [3L]                                                                                                               | Instruction set of 8085<br>microprocessor, Addressing<br>modes and Timing diagram of<br>the instructions (a few<br>examples) has been placed in<br>Module 2.<br>Interrupts of 8085 processor<br>(software and hardware), I/O<br>Device Interfacing-I/O Mapped<br>I/O and Memory Mapped I/O<br>has been shifted in Module 1.<br>Serial (using SID and SOD<br>pins and RIM, SIM<br>Instructions) and Parallel data<br>transfer part has been omitted. | 8085<br>Hardware<br>model and<br>software<br>model has<br>been placed<br>in separate<br>modules | Module -2: [11L]<br>Instruction set of 8085 microprocessor,<br>Addressing modes. [3L]<br>Assembly language programming with<br>examples, Counter and Time Delays, Stack<br>and Subroutine. [6L]<br>Timing diagram of the instructions (a few<br>examples) [2L]                                                                                                                                                                                                                              |

| 3   | 8      | Module -3 [10L]<br>The 8086 microprocessor- Architecture,<br>Addressing modes, Interrupts [3L]<br>Introduction to 8051 Microcontroller –<br>Architecture, Pin Details. [3L]<br>Addressing modes, Instruction set,<br>Examples of Simple Assembly Language.<br>[4L]                                                                                                                                                                                                      | Pin Details of 8086<br>microprocessor has been added.<br>Instruction set, Examples of<br>Simple Assembly Language<br>and Memory interfacing with<br>8086 has been added.<br>Introduction to 8051<br>Microcontroller –Architecture,<br>Pin Details.<br>Addressing modes, Instruction<br>set, Examples of Simple<br>Assembly Language have been<br>shifted to Module 4                                                                                | A dedicated<br>module is<br>for only<br>8086                                                    | Module 3: [8L]<br>The 8086 microprocessor- Architecture, Pin<br>Details, Addressing modes, Interrupts [3L]<br>Instruction set, Examples of Simple Assembly<br>Language [3L]<br>Memory interfacing with 8086 [2L]                                                                                                                                                                                                                                                                            |

| 4   | 7      | Module -4: [9L]<br>Memory interfacing with 8085, 8086 [2L]<br>Support IC chips- 8255<br>,8251,8237/8257,8259 [4L]<br>Interfacing of 8255 PPI with 8085 and<br>Microcontroller 8051. [2L]<br>Brief introduction to PIC microcontroller<br>(16F877) [1L]                                                                                                                                                                                                                  | Memory interfacing with 8085<br>has been shifted to Module 1<br>Memory interfacing with 8086<br>has been shifted to Module 3<br>Rest are omitted                                                                                                                                                                                                                                                                                                    | A dedicated<br>module is<br>for only<br>8051                                                    | Module -4: [7L]<br>Introduction to 8051 Microcontroller –<br>Architecture, Pin Details. [3L]<br>Addressing modes, Instruction set, Examples<br>of Simple Assembly Language. [4L]                                                                                                                                                                                                                                                                                                            |

# MODULE 1

# LECTURE 1: ARCHITECTURE OF 8085 MICROPROCESSOR (PIN DESCRIPTION)

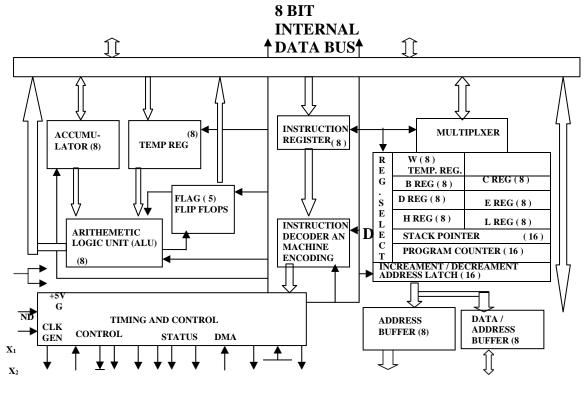

## 1. ARCHITECTURE AND PIN DESCRIPTION OF 8085 MICROPROCESSOR

The 8085 is an 8-bit general purpose microprocessor capable of addressing 64K of memory. The device has forty pins, requires a +5V single power supply, and can operate with a 3MHz single phase clock.

Following Figure (Figure 1.1) shows the pin diagram of 8085 Microprocessor.

| Y N                                           | 1  | 40 Vcc               |

|-----------------------------------------------|----|----------------------|

|                                               | '  | P                    |

| $X_2 \longrightarrow C$                       | 2  | 39 HOLD              |

| Reset out                                     | 3  | 38 HLDA              |

| SOD 🗲 🔤                                       | 4  | 37]> CLK (out)       |

| SID                                           | 5  | 36] - Reset in       |

| Trap 🗲 –[                                     | 6  | 35] - Ready          |

| RST 7.5                                       | 7  | 34]► IO/M            |

| RST 6.5 🗲[                                    | 8  | 33]S <sub>1</sub>    |

| RST 5.5                                       | 9  | 32] - Vpp            |

|                                               | 10 | 31]                  |

|                                               | 11 | 30]                  |

|                                               | 12 | 29] → S <sub>0</sub> |

| AD <sub>1</sub>                               | 13 | 28] A <sub>15</sub>  |

| $AD_2 \blacksquare$                           | 14 | 27 A14               |

| $AD_3 \blacktriangleleft \blacktriangleright$ | 15 | 26] A <sub>13</sub>  |

|                                               | 16 | 25] A12              |

|                                               | 17 | 24] A11              |

|                                               | 18 | 23] A10              |

|                                               | 19 | 22] — A <sub>9</sub> |

| Vss —                                         | 20 | 21 A <sub>8</sub>    |

|                                               |    |                      |

Figure 1.1

All the signals can be classified into six groups.

- 1. Address bus

- 2. Data bus

- 3. Control and status signals

- 4. Power supply and frequency signals

- 5. Externally initiated signals

- 6. Serial I/O ports.

Here details of individual pins are described.

Pin number:

- 1. X1 (Input)

- 2. X2 (Input)

An LC tuned circuit or an RC network or a crystal (X-tal) can generate clock pulses. In 8085 MPU, an X-tal is connected at these two pins (pin number 1 and 2). The clock generation circuitry is built inside the unit. The crystal frequency must be at least 1 MHz. The operating frequency of 8085 is 6 MHz. Special variant 8085 is operated with a 10 MHz crystal. The output pulse train got from crystal is not exact square pulse. So certain amount of wave-shaping is required. The wave-shaping circuit may be Smitt-trigger circuit using OP\_AMP. Smitt-trigger circuit behaves like a flip-flop (divide by 2) circuit. Thus the frequency at which microprocessor operates is half of the crystal frequency. Hence we can say 8085 operates with 3 MHz clock frequency.

3. RESET OUT (Output)

The "Reset Out" pin gives a signal that indicates that the MPU is being reset. The same signal can be used to reset (or acknowledge) the various other peripheral devices.

- 4. SOD (Output)

- 5. SID (Input)

The 8085 has two signals to implement the serial transmission: SOD (Serial Output Data) and SID (Serial Input Data). In serial transmission, data bits are sent over a single line, one bit at a time, such as transmission over telephone lines. The data on SID pin is loaded into Accumulator bit B7 whenever a RIM instruction is executed. The output SOD is set or reset as specified by the SIM instruction.

TRAP (Input)

RST7.5 (Input)

RST6.5 (Input)

RST5.5 (Input)

INTR (Input)

INTA' (Output)

TRAP, RST7.5, RST6.5, RST5.5 and INTR are interrupt signals and INTA' is active low interrupt acknowledge signal.

We shall present a discussion about "Interrupt" later.

AD0 (Input / Output)

AD1 (Input / Output)

AD2 (Input / Output)

AD3 (Input / Output)

AD4 (Input / Output)

AD5 (Input / Output)

AD6 (Input / Output)

AD7 (Input / Output)

The signal lines AD7 - AD0 are bidirectional: they serve a dual purpose. They are used as the low-order address bus as well as the data bus. In executing an instruction, during the earlier part of the cycle, these lines are used as the low-order address bus. During the later part of the cycle, these lines are used as the data bus. (This is also known as multiplexing the bus.)

Low-order address bus and data bus are mutually exclusive, i.e., these are not needed simultaneously.

Pin Number:

20. GND

Pin number 20 is connected with Ground.

Pin Number:

21. A8 (Output)

22. A9 (Output)

23. A10 (Output)

24. A11 (Output)

25. A12 (Output)

26. A13 (Output)

27. A14 (Output)

28. A15 (Output)

The 8085 has these eight signal lines, A15 - A8, which are unidirectional and used as the high-order address bus (the most significant 8 bits of the address bus).

Pin Number:

29. S0 (Output)

S0 is status signal used to identify the nature of the operation.

Pin Number:

30. ALE (Output)

The ALE (Address Latch Enable) signal is used to demultiplex the low-order bus (the least significant 8 bits of the address bus). Logic 1 on this pin indicates that the bits on AD7 - AD0 are address bits. Logic 0 on this pin indicates that AD7-AD0 contain data.

Pin Number:

31. WR' (Output) 32. RD' (Output)

WR' is a Write control signal (active low). This signal indicates the data on the data bus are to be written into a selected memory or I/O location.

RD' is a Read control signal (active low). This signal indicates that the selected I/O or memory device is to be read and data are available on the data bus.

RD' and WR' are mutually exclusive signals. Both of them can be inactive at the same time but both of them cannot be active at the same time.

Pin Number:

33. S1 (Output)

S0 is status signal used to identify the nature of the operation.

Pin Number:

34. IO / M' (Output)

This is a status signal used to differentiate between I / O and memory operations. When it is HIGH, it indicates an I/O operation; when it is LOW, it indicates a memory operation.

#### Pin Number:

35. READY (Input)

The MPU checks the status of this pin after every machine cycle within a particular instruction. If READY pin is found HIGH, then the MPU proceeds to the next instruction; otherwise, it waits over there and starts checking the status of this READY pin after every clock cycle till found HIGH.

The functions of READY pin are:

- i. We can introduce some sort of wait cycles within instruction.

- The READY pin is used for matching and speed synchronization between MPU and peripheral device(s). For example, we can synchronize a slower printer with a MPU. Here, READY signal is used to delay the microprocessor read or write cycles until the printer (a slow-responding peripheral) is ready to send or accept data.

#### Pin Number:

36. RESET IN' (Input)

When the signal on pin 36 goes low then

- i. The PC is set to zero

- ii. The buses are tri-stated

- iii. Flip-flops are cleared

- iv. Registers are cleared

- v. The MPU is reset

Pin Number:

37. CLK (Output)

The Clock Output signal is supplied to all peripheral devices. This will be 3 MHz for 8085.

Pin Number:

38. HLDA (Output)39. HLD (Input)

When HLD (Hold) signal is HIGH, MPU is reset and buses are not tri-stated. This signal indicates that a peripheral such as a DMA controller is requesting the use of the address and data buses, i.e. DMA transfer can be done when HLD is HIGH.

An acknowledge signal (HLDA) is needed to synchronize the MPU with DMA controller. HLDA signal acknowledges the Hold request.

Pin Number:

40. Vcc

This is +5V power supply.

# **LECTURE 2: INTERRUPTS IN 8085**

## 2. INTERRUPTS IN 8085

The interrupt I/O is a process of data transfer whereby an external device or a peripheral can inform the processor that is ready for communication and it requests attention. The process is initiated by an external device and is asynchronous which means that it can be initiated at any time without reference to the system clock. However, the response to an interrupt request is directed o controlled by the microprocessor.

## **Interrupt – Hardware Interrupt and Software Interrupt:**

Hardware Interrupts are interrupts which are non-deterministic, i.e., their time of occurrence is unknown to us. Hardware interrupts may be generated due to power-off. [Examples: TRAP, RST7.5, RST6.5, RST5.5and INTR].

Software interrupts are interrupts which are deterministic. RST instructions are commonly used to set up software breakpoints. [Examples: RST0, RST1, RST2, RST3, RST4, RST5, RST6, RST7].

#### Interrupt - Vectored Interrupt and Non-vectored Interrupt:

In case of vectored interrupt, the MPU knows which device is asking for interrupt, i.e., where to jump. The PC jumps to a specific predefined memory location. [Examples: TRAP, RST7.5, RST6.5, RST5.5, RST0, RST1, RST2, RST3, RST4, RST5, RST6 and RST7].

In case of non-vectored interrupts, the MPU does not know where to jump. If a single interrupt line is connected with a number of devices, then this type of interrupt takes place. In this case, the MPU has to go in a procedure called Daisy Polling Chain, where the device near to MPU gets priority. [Example: INTR].

## Vectored Interrupts:

The 8085 instruction set includes eight RST (RESTART) instructions. These are 1-byte call instructions that transfers the program execution to a specific location on page 00H., i.e., that compel the PC to jump to the memory location whose address is predefined, as listed in following table [Table 1.1]:

| Instructions | Call Location (in Hex) |

|--------------|------------------------|

| RST0         | 0000                   |

| RST1         | 0008                   |

| RST2         | 0010                   |

| RST3         | 0018                   |

| RST4         | 0020                   |

| RST5 | 0028 |

|------|------|

| RST6 | 0030 |

| RST7 | 0038 |

#### Table 1.1: Vectored Software Interrupts

Again, the 8085 has four hardware vectored interrupts. These are TRAP, RST7.5, RST6.5 and RST5.5. These four are automatically vectored (transferred) to specific locations on memory page 00H without any external hardware. The necessary hardware is already implemented inside the 8085 MPU. These interrupts and their call locations are listed below [Table 1.2]:

| Interrupts | Call Location (in Hex) |

|------------|------------------------|

| TRAP       | 0024                   |

| RST7.5     | 003C                   |

| RST6.5     | 0034                   |

| RST5.5     | 002C                   |

Table 1.2: Vectored Software Interrupts

Now we can list all the vector interrupts and their corresponding call locations in a single table. The table is listed below [Table 1.3]:

| Instructions | Call Location (in Hex) |

|--------------|------------------------|

| RST0         | 0000                   |

| RST1         | 0008                   |

| RST2         | 0010                   |

| RST3         | 0018                   |

| RST4         | 0020                   |

| TRAP         | 0024                   |

| RST5         | 0028                   |

| RST5.5       | 002C                   |

| RST6         | 0030                   |

| RST6.5       | 0034                   |

| RST7         | 0038                   |

| RST7.5       | 003C                   |

Table 1.3: Vectored Software Interrupts

If Interrupt Service Routine (ISR) is written in memory location whose address is between two call locations of interrupts, then 8 bytes / 4 bytes are not sufficient for writing ISR. Hence we can take help of jump instruction 'JMP'. This jump instruction (3-byte instruction) actually compels the PC to jump to the memory location whose address is given or specified, and at that memory location full length ISR is written. These memory locations are usually ROM locations.

We can take an example. Let the instruction "RST5" is written within a program. When the processor encounters this instruction, the program is transferred to location 0028H. The ISR is written somewhere else in memory (let between 2000 and 2100), and the jump instruction is written at 0028 to specify the address (i.e., between 2000 and 21000 of the ISR.

[Between 2000 and 2100, some ISRs are loaded by the monitor program when the machine gets loaded.]

Non- Vectored Interrupts:

Non-vectored interrupted are processed through a mechanism called Daisy Polling Chain. In 8085, INTR is the only non-vectored interrupt and INTA' is the interrupt acknowledge (active low).

#### **Interrupt – Maskable Interrupt and Non-maskable Interrupt:**

The MPU can ignore or delay a certain interrupt at certain time when it is performing some critical task. This is maskable interrupt. [Examples: RST7.5, RST6.5, RST5.5, RST0, RST1, RST2, RST3, RST4, RST5, RST6, RST7, INTR].

The MPU has to respond a certain type of interrupt request immediately. This is non-maskable interrupt. [Example: TRAP]

#### **Interrupts based on Priority:**

- i. Vectored interrupt gets higher priority than non-vectored interrupts.

- ii. As far as software interrupts are concerned, there is no priority because it is known when the interrupts is going to take place.

- iii. Hardware interrupts with higher number gets higher priority. But TRAP is exceptional. TRAP has the highest priority

- iv. Vectored interrupts with higher number gets higher priority. But TRAP is exceptional. TRAP has the highest priority. For example, between RST7.5 and RST7, the first one gets higher priority.

# **LECTURE 3: INSTRUCTIONS ABOUT INTERRUPTS IN 8085**

## 3. THE INSTRUCTIONS ABOUT INTERRUTPS

The 8085 interrupt process is controlled by the Interrupt Enable flip-flop, which is internal to the processor and can be set or reset by using software instructions. If the flip-flop is enabled and the input to the interrupt signal goes high, the microprocessor is interrupted.

The interrupt process should be enabled by writing the instruction EI in the main program. The instruction EI sets the Interrupt Enable Flip-Flop. The instruction DI resets the FF and disables the interrupt process.

Instruction

EI (Enable Interrupt)

- This is 1-byte instruction.

- The instruction sets the Interrupt Enable FF and enables the Interrupt process.

- System reset or an interrupt disables the interrupt disables the interrupt process.

#### Instruction

DI (Disable Interrupt)

- This is 1-byte instruction.

- The instruction resets the Interrupt Enable FF and disables the interrupt process.

- It should be included in a program segment where an interrupt from an outside source cannot be tolerated.

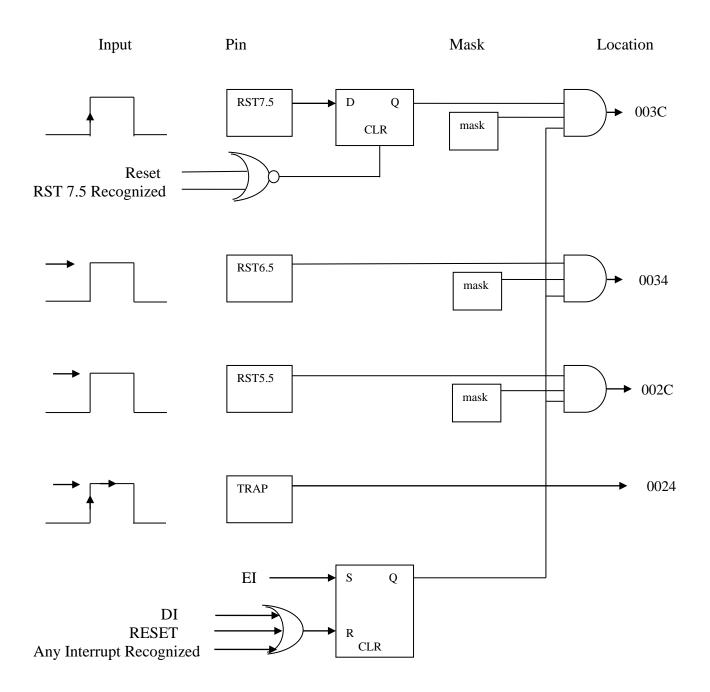

The 8085 has five interrupt inputs (Figure). One is called INTR, three are called RST5.5, RST6.5 and RST7.5, respectively, and the fifth is called TRAP, a non-maskable interrupt.

The TRAP has the highest priority, followed by RST7.5, RST6.5, RST5.5 and INTR, in that order. [However, the TRAP has a lower priority than the Hold signal used for DMA].

TRAP is a non-maskable interrupt. It has the highest priority among the interrupt signals, it need not be enabled and it cannot be disabled. It is level and edge-sensitive, meaning that the input should go high and stay high to be acknowledged. It cannot be acknowledged. It cannot be acknowledged again until it makes a transition from high to low to high.

Figure 1.2 shows that when this interrupt is triggered, the program control is transferred to location 0024 without any external hardware or the interrupt enable instruction EI. TRAP is generally used for such critical events as power failure and emergency shut-off.

Figure 1.2: Hardware for 8085 Vectored Interrupts

RST 7.5, RST6.5 and RST5.5

The maskable interrupts RST7.5, RST6.5 and RST5.5 (shown in Figure) are enabled under program control with two instructions: EI (Enable Interrupt) described earlier and SIM (Set Interrupt Mask) described below:

Instruction

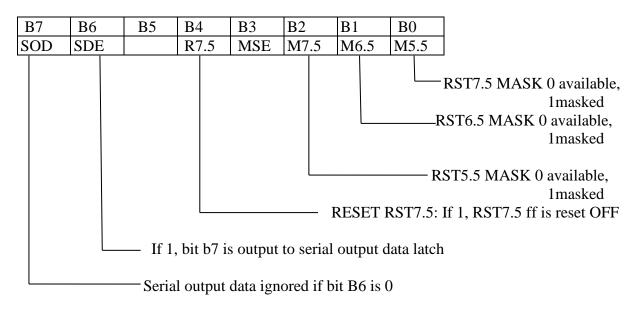

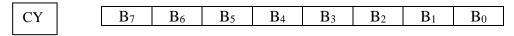

SIM (Set Interrupt Mask)

- This is 1-byte instruction.

- The instruction can be used for three different functions

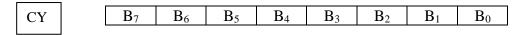

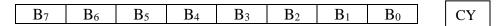

- i) One function is to set mask for RST7.5, rst6.5 and rst5.5 interrupts. This instruction reads the content of the accumulator and enables or disables the interrupts according to the content of the accumulator. Bit B3 is control bit and should be equal to 1 for bits B0, B1 and B2 to be effective. Logic 0 on B0, B1 and B2 will enable the corresponding interrupts and logic 1 will disable the interrupts.

- ii) The second function is to reset RST7.5 FF. Bit B4 is additional control for RST7.5. If B4 is , RST7.5 is reset. This is used to override (or ignore) RST7.5 without servicing it.

- iii) The third function is to implement serial I/O. Bits B7 and B6 of the accumulator are used for serial I/O and do not affect the interrupts. Bit B6 = 1 enables the serial I/O and bit B7 is used to transmit (output) bits.

Figure 1.3: SIM INSTRUCTION FORMAT

Here we are concerned with RST7.5, RST6.5 and RST5.5 interrupts and not with serial I/O.

How interrupt process is done in the 8085 is described below:

1. The interrupt process is enabled. The instruction EI sets the Interrupt Enable FF and one of the inputs to the AND gates is set to logic 1. These AND gates activate the program transfer to various vectored locations.

#### Paper Code: CS602

- 2. An appropriate bit pattern is loaded into the accumulator.

- 3. If bit B3 is 1, the respective interrupts are enabled according to bits B2-B0.

- 4. RST7.5, RST6.5 and RST5.5 interrupts are being monitored.

- 5. If bit B3 is 0, bits B2-B0 have no effect on previous conditions.

- 6. Bit B4 is 1. This resets RST7.5.

The entire interrupt process (except TRAP) is disabled by resetting the Interrupt Enable FF. The FF can be reset in one of the following three ways:

- Instruction DI •

- System Reset ٠

- Recognition of an interrupt request

Figure shows that these three signals are ORed and the output of the OR gate is used to reset the FF.

**Triggering Levels:**

These interrupts are sensitive to different types of triggering as listed below:

RST7.5: This is positive-edge sensitive and can be triggered with a short pulse. The request is stored internally by the D flip-flop (Figure) until the microprocessor responds to the request or until it is cleared by Reset or by bit B4 in the SIM instruction.

RST6.5 and RST5.5: these interrupts are level-sensitive, meaning that the triggering level should be on until the microprocessor completes the execution of the current instruction. If the microprocessor is unable to respond to these requests immediately, they should be stored or held by external hardware.

Pending Interrupts:

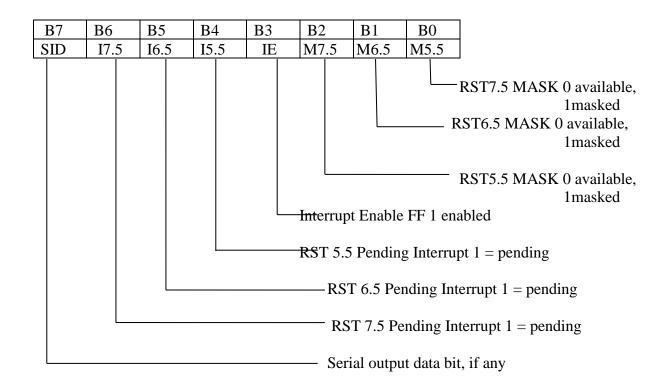

Because there are several interrupt lines, when one interrupt request is being served, other interrupt request may occur and remain pending. The 8085 has an additional instruction called RIM (Read Interrupt Mask) to sense these pending interrupts.

Instruction

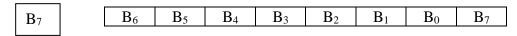

**RIM: Read Interrupt Mask**

- This is 1-byte instruction.

- The instruction can be used for the following functions

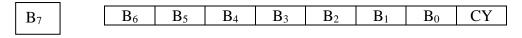

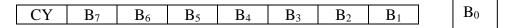

- i) To read interrupt masks. This instruction loads the accumulator with 8 bits indicating the current status of the interrupt masks (Figure).

- ii) To identify pending interrupts. Bit B4, B5 and B6 (Figure) identify the pending interrupts.

- To receive serial data. Bit B7 (Figure) is used to receive serial data. iii)

Figure 1.4: RIM INSTRUCTION FORMAT

# **LECTURE 4: ADDRESS / DATA BUS DEMULTIPLEXING**

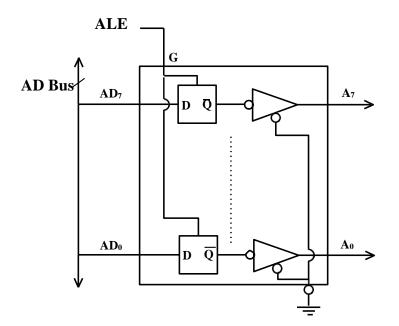

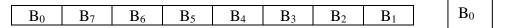

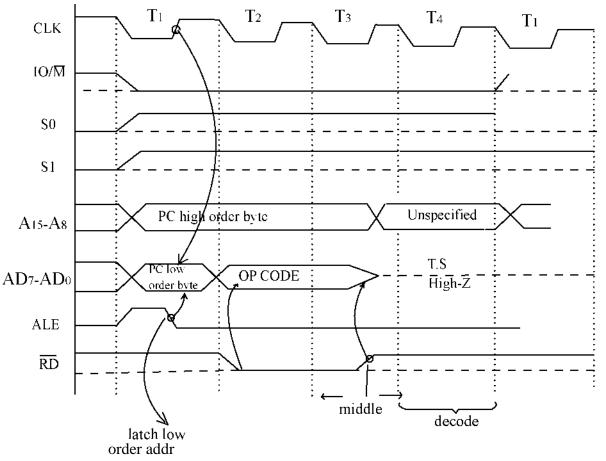

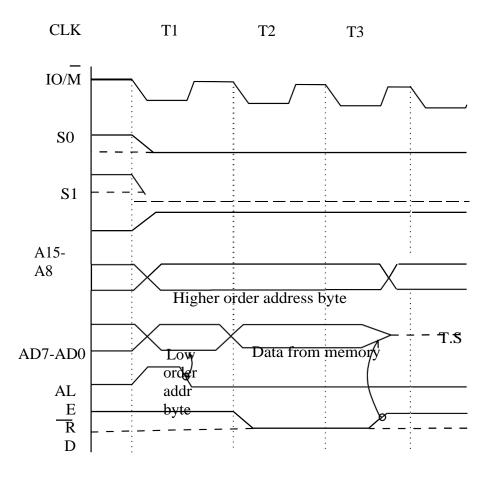

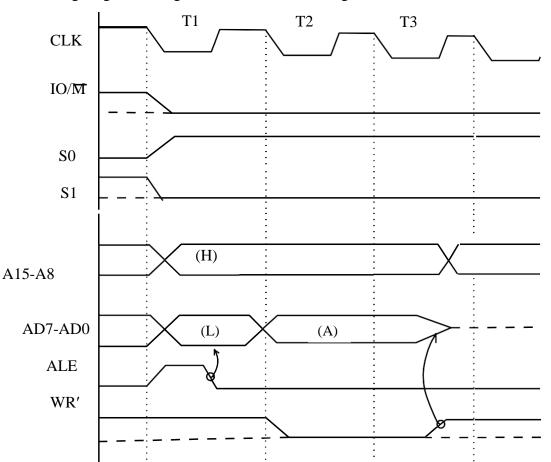

The 8085 uses a time multiplexed address-data bus. This is due to limited number of pins on the 8085. Low-order 8-bits of the address appear on the AD bus during the first clock cycle i.e.,  $T_1$  state of a machine cycle. It then becomes the data bus during the second and third clock cycles i.e.,  $T_2$  and  $T_3$ states.

ALE stands for address latch enable. It is used to distinguish whether the  $AD_7 - AD_0$  bus contains address bits  $A_7 - A_0$  or data bits  $D_7$ -  $D_0$ . It is a single pulse issued during every  $T_1$  state of the microprocessor

Since the lower 8-bits of the address information  $A_7$  to  $A_0$  is available at pin no.19 to pin no.12 only during  $T_1$  period, therefore, ALE pulse can be can be used to latch address  $A_7$  to  $A_0$  in an external latch. ALE output is high during first half of the  $T_1$  period and its falling edge can be used to latch the address bits  $A_7$  to  $A_0$  in an external latch e.g. 74LS373 register latch.

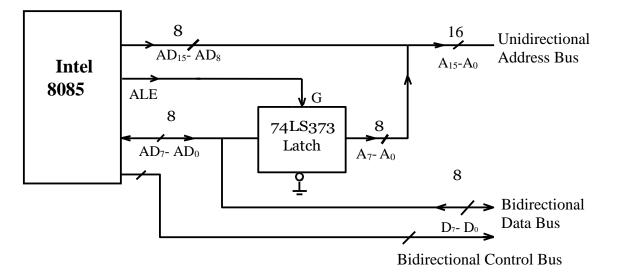

Fig.1.5a shows a schematic that uses a latch and the ALE signal to de multiplex the bus. The bus  $AD_7-AD_0$  is connected as the input to the latch 74LS373. The ALE signal is connected to the enable (G) pin of the latch, and the output control (OC) signal of the latch is grounded. When ALE goes high during the T<sub>1</sub> state of a machine cycle, the latch is transparent and the output of the latch changes according to the input. The CPU is putting lower-order bits of address during this time. When the ALE goes LOW, the address bits get latched on the output and remain so until the next ALE signal.

## Online Courseware for B.Tech. Computer Science and Engineering Program (Autonomy) Paper Name: Microprocessor and Microcontrollers Paper Code: CS602 Fig.1.5a: Latching of Lower Order Address in External Latch

Once saved in an external latch the lower order address  $A_7$  to  $A_0$  shall be available at the output of the register latch for the subsequent states  $T_2$ ,  $T_3$ ,  $T_4$ ,  $T_5$  &  $T_6$ , while pin no. 19 to pin no.12 can then be utilized by the microprocessor for bi-directional operation. The falling edge of the ALE can also be used to store status information being output by the 8085 during each machine cycle. The ALE output is never tri-stated in the 8085. The manner of utilization of pins 19 to 12 is known as time multiplexed mode of operation.

The de-multiplexing of AD bus by latching lower byte of 16-bit address in external 8-bit latch 74LS373 is shown in Fig.1.5b. Once the lower byte address is latched, the AD bus is available for bi- directional data transfer. The 8-bit higher order address issued by microprocessor in every T1 state along with latched lower byte address constitutes unidirectional 16-bit address bus. The control signals put together constitutes bi-directional control bus, where some of the signals are always input and some are always output. The three buses, address bus, data bus and control bus together constitutes system bus.

Fig.1.5b: De-multiplexing of AD bus to Generate System Bus

The fact that ALE is required is a direct consequence of having a multiplexed data/address bus. This is unlike the Intel 8080 microprocessor which is similar to the 8085 but where these buses are not multiplexed. Some of the peripheral chips 8155/ 8156/ 8355/ 8755A have internal multiplexing facility, therefore, ALE input pin of these peripheral chips is connected to ALE output pin of the 8085, thus allowing a direct interface with the 8085. Thus IC chips internally de-multiplex the AD bus using the ALE signal. Since a majority of peripheral devices do not have the internal multiplexing facility, there is external hardware necessity for it.

# MODULE 2

# LECTURE 1: INTRODUCTION TO 8085 PROGRAMMING MODEL

## 1. THE 8085 PROGRAMMING MODEL

The 8085 programming model includes six registers, one accumulator, and one flag register, Figure. In addition, it has two 16-bit registers: the stack pointer and the program counter. They are described briefly as follows

| ACCUMULATOF                | R (8) FLAG (8)            |             |  |  |  |

|----------------------------|---------------------------|-------------|--|--|--|

| B (8)                      | C (8)                     |             |  |  |  |

| D (8)                      | E (8)                     |             |  |  |  |

| H (8)                      | L (8)                     |             |  |  |  |

| Stack Pointer (16)         | •                         |             |  |  |  |

| Program Counter (          | Program Counter (16)      |             |  |  |  |

| 8-lines bidirectional data | bus 16-bit unidirectional | address bus |  |  |  |

Figure 2.1: 8085 Programming Model

## Registers

The 8085 has six general-purpose registers to store 8-bit data; these are identified as B,C,D,E,H, and L as shown in the figure. They can be combined as register pairs - BC, DE, and HL - to perform some 16-bit operations. The programmer can use these registers to store or copy data into the registers by using data copy instructions.

## Accumulator

The accumulator is an 8-bit register that is a part of arithmetic/logic unit (ALU). This register is used to store 8-bit data and to perform arithmetic and logical operations. The result of an operation is stored in the accumulator. The accumulator is also identified as register A.

#### Flags

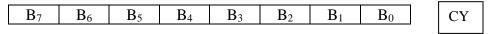

The ALU includes five flip-flops, which are set or reset after an operation according to data conditions of the result in the accumulator and other registers. They are called Zero (Z), Carry (CY), Sign (S), Parity (P), and Auxiliary Carry (AC) flags; their bit positions in the flag register are shown in the Figure below. The most commonly used flags are Zero, Carry, and Sign. The microprocessor uses these flags to test data conditions.

| B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|----|----|----|----|----|----|----|----|

| S  | Ζ  |    | AC |    | Р  |    | CY |

Figure 2.1: 8085 Flag Register

For example, after an addition of two numbers, if the sum in the accumulator id larger than eight bits, the flip-flop uses to indicate a carry – called the Carry flag (CY) – is set to one. When an arithmetic operation results in zero, the flip-flop called the Zero (Z) flag is set to one. The first Figure shows an 8-bit register, called the flag register, adjacent to the accumulator. However, it is not used as a register; five bit positions out of eight are used to store the outputs of the five flip-flops. The flags are stored in the 8-bit register so that the programmer can examine these flags (data conditions) by accessing the register through an instruction.

These flags have critical importance in the decision-making process of the microprocessor. The conditions (set or reset) of the flags are tested through the software instructions. For example, the instruction JC (Jump on Carry) is implemented to change the sequence of a program when CY flag is set. The thorough understanding of flag is essential in writing assembly language programs.

**Sign Flag (S)** – After any operation if the MSB (B(7)) of the result is 1, it in indicates the number is negative and the sign flag becomes set, i.e. 1. If the MSB is 0, it indicates the number is positive and the sign flag becomes reset i.e. 0.

from 00H to 7F, sign flag is 0 from 80H to FF, sign flag is 1

1- MSB is 1 (negative) 0- MSB is 0 (positive)

#### **Example:**

MVI A 30 (load 30H in register A) MVI B 40 (load 40H in register B) SUB B (A = A - B) These set of instructions will set the sign flag to 1 as 30 – 40 is a negative number.

- MVI A 40 (load 40H in register A) MVI B 30 (load 30H in register B) SUB B (A = A - B) These set of instructions will reset the sign flag to 0 as 40 - 30 is a negative number.

- 2. **Zero Flag (Z)** After any arithmetical or logical operation if the result is 0 (00)H, the zero flag becomes set i.e. 1, otherwise it becomes reset i.e. 0.

00H zero flag is 1.

from 01H to FFH zero flag is 0

1- zero result

0- non-zero result

## **Example:**

MVI Å 10 (load 10H in register A) SUB A (A = A – A) These set of instructions will set the zero flag to 1 as 10H - 10H is 00H

3. Auxiliary Cary Flag (AC) – This flag is used in BCD number system (0-9). If after any arithmetic or logical operation D(3) generates any carry and passes on to B(4) this flag becomes set i.e. 1, otherwise it becomes reset i.e. 0. This is the only flag register which is not accessible by the programmer

1-carry out from bit 3 on addition or borrow into bit 3 on subtraction 0-otherwise

#### **Example:**

MOV A 2B (load 2BH in register A) MOV B 39 (load 39H in register B) ADD B (A = A + B)

These set of instructions will set the auxiliary carry flag to 1, as on adding 2B and 39, addition of lower order nibbles B and 9 will generate a carry.

4. **Parity Flag (P)** – If after any arithmetic or logical operation the result has even parity, an even number of 1 bits, the parity register becomes set i.e. 1, otherwise it becomes reset i.e. 0.

1-accumulator has even number of 1 bits 0-accumulator has odd parity

## Example:

MVI A 05 (load 05H in register A)

This instruction will set the parity flag to 1 as the BCD code of 05H is 00000101, which contains even number of ones i.e. 2.

5. Carry Flag (CY) – Carry is generated when performing n bit operations and the result is more than n bits, then this flag becomes set i.e. 1, otherwise it becomes reset i.e. 0. During subtraction (A-B), if A>B it becomes reset and if (A<B) it becomes set. Carry flag is also called borrow flag.

1-carry out from MSB bit on addition or borrow into MSB bit on subtraction 0-no carry out or borrow into MSB bit

#### **Example:**

MVI A 30 (load 30H in register A) MVI B 40 (load 40H in register B) SUB B (A = A - B)

These set of instructions will set the carry flag to 1 as 30 - 40 generates a carry/borrow.

MVI A 40 (load 40H in register A) MVI B 30 (load 30H in register B) SUB B (A = A - B)

These set of instructions will reset the sign flag to 0 as 40 - 30 does not generate any carry/borrow.

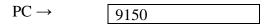

## **Program Counter (PC)**

This 16-bit register deals with sequencing the execution of instructions. This register is a memory pointer. Memory locations have 16-bit addresses, and that is why this is a 16-bit register. The microprocessor uses this register to sequence the execution of the instructions. The function of the program counter is to point to the memory address from which the next byte is to be fetched. When a byte (machine code) is being fetched, the program counter is incremented by one to point to the next memory location.

#### Stack Pointer (SP)

The stack pointer is also a 16-bit register used as a memory pointer. It points to a memory location in R/W memory, called the stack. The beginning of the stack is defined by loading 16-bit address in the stack pointer.

This programming model will be used in subsequent tutorials to examine how these registers are affected after the execution of an instruction.

# **LECTURE 2: ADDRESSING MODES IN 8085**

## 2. ADDRESSING MODES IN 8085

These are the instructions used to transfer the data from one register to another register, from the memory to the register, and from the register to the memory without any alteration in the content. Addressing modes in 8085 is classified into 5 groups -

## Immediate addressing mode

In this mode, the 8/16-bit data is specified in the instruction itself as one of its operand. For example: MVI C, 20F: means 20F is copied into register C.

## **Register addressing mode**

In this mode, the data is copied from one register to another. For example: MOV D, B: means data in register B is copied to register D.

## **Direct addressing mode**

In this mode, the data is directly copied from the given address to the register. For example: LDA 5000: means the data at address 5000 is copied to register A.

## Indirect addressing mode

In this mode, the data is transferred from one register to another by using the address pointed by the register.

For example: LDAX B: means data is transferred from the memory address pointed by the register pair BC to the register A.

## Implied addressing mode

This mode doesn't require any operand; the data is specified by the opcode itself. For example: CMA.

# LECTURE 3: INSTRUCTION SET (DATA TRANSFER INSTRUCTION)

## 3. THE 8085 INSTRUCTIONS:

The 8085 instructions can be classified into the following five functional categories: data transfer (copy) operations, arithmetic operations, logical operations, branching operations and machine-control operations.

## **3.1.DATA TRANSFER (COPY) INSTRUCTION**

This group of instructions copies data for a location (register or I/O or memory) called the source, to another location (register or I/O or memory) called the destination. The contents of the source are not changed. In the8085 processor, data transfer instructions do not affect the flags. The instructions used to copy are:

- 1. MOV

- 2. MVI

- 3. LXI

- 4. LDA

- 5. STA

- 6. LDAX

- 7. STAX

- 8. LHLD

- 9. SHLD

- 10. XCHG

- 11. IN

- 12. OUT

#### 1. MOV: Move - Copy from Source to Destination

| Opcode | Operand | Bytes | Register Transfer Logic          |

|--------|---------|-------|----------------------------------|

| MOV    | Rd, Rs  | 1     | (Rd) (Rs)                        |

| MOV    | M, Rs   | 1     | ((H)(L)) ← (Rs)                  |

| MOV    | Rd,M    | 1     | $(Rd)  \longleftarrow  ((H)(L))$ |

Description: This instruction copies the contents of the source register into the destination register, the content of the source register are not altered. If one of the operands is a memory location, it is specified by the contents of HL registers.

Flags: No flags are affected

#### Example 1:

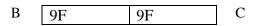

Let us assume register B contains 72H and register C contains 9F. We move the contents of

register C to register B.

Instruction: MOV B, C

It can be noted that the first operand B specifies the destination and the second operand C specifies the source.

Register contents before instruction

B 72 9F C

Register contents before instruction

## Example 2:

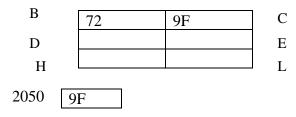

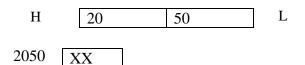

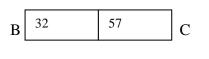

Let us assume register B contains 72H and registers H and L are 20 and 50, respectively. Memory location 2050 contains 9F. We transfer the contents of the memory location to register B.

Instruction: MOV B, M

Contents before instruction

Contents after instruction

## 2. MVI: Move Immediate 8-bit

| Opcode | Operand           | Bytes | Register Transfer Logic  |

|--------|-------------------|-------|--------------------------|

| MVI    | Rd, <data></data> | 2     | (Rd) ← <data></data>     |

| MVI    | M, <data></data>  | 2     | ((H)(L)) ← <data></data> |

Description: The 8-bit data are stored in the destination register or memory. If the operand is a memory location, it is specified by the contents of HL registers.

Flags: No flags are affected

## Example 1:

Let us load 92 in register B

Instruction: MVI B, 92

This instruction loads 92 in register B.

## Example 2:

Let us assume that registers H and L contain 20 and 50, respectively. We want to load 3A in memory location 2050.

Instruction: MVI M, 3A

Contents before instruction

Contents after instruction

2050 3A

#### 3. LXI: Load Register pair Immediate

| Opcode | Operand                  | Bytes | Register Transfer Logic |

|--------|--------------------------|-------|-------------------------|

| LXI    | Reg. Pair, <16-bit data> | 3     | (Rl)                    |

|        |                          |       | (Rh) - Byteh            |

Description: The instruction loads 16-bit data in the register pair designated in the operand. This is a 3-byte instruction; the second byte specifies the low-order byte and the third byte specifies the high-order byte.

Flags: No flags are affected

## Example :

We want to load the 16-bit data 2050 in register pair BC.

Instruction: LXI B, 2050

This instruction loads 50 in register C and 20 in register B.

[Comments: We can note the reverse order in entering the code of 16-bit data. This is the only instruction that can directly load a 16-bit address in the stack pointer register.]

## 4. LDA: Load Accumulator Direct

| Opcode | Operand          | Bytes | Register Transfer Logic           |

|--------|------------------|-------|-----------------------------------|

| LDA    | <16-bit address> | 3     | (A) $\leftarrow$ (16-bit address) |

Description: The contents of a memory location, specified by a 16-bit address in the operand, are copied to the accumulator. The contents of the source are not altered. This is a 3-byte instruction; the second byte specifies the low-order address and the third byte specifies the high-order address.

Flags: No flags are affected

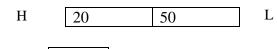

#### Example :

Let us assume memory location 9050 contains byte F8. We want to load the accumulator with the contents of location 9050.

Instruction: LDA 2050

Contents before instruction

F A FF XX

9050 XX

Contents after instruction

F8

A FF XX F

9050

# 5. STA: Store Accumulator Direct

| Opcode | Operand          | Bytes | Register Transfer Logic |

|--------|------------------|-------|-------------------------|

| STA    | <16-bit address> | 3     | (16-bit address) ← (A)  |

Description: The contents of the accumulator are copied to a memory location specified the operand, are copied to a memory location specified by the operand. This is a 3-byte instruction; the second byte specifies the low-order address and the third byte specifies the high-order address.

Flags: No flags are affected

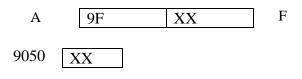

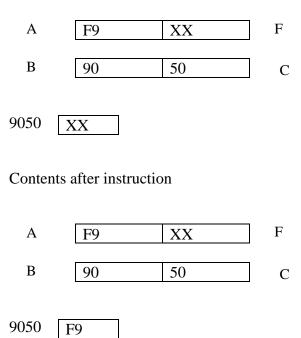

#### **Example:**

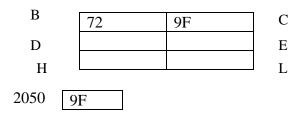

Let the accumulator contains byte 9F. We want to store the accumulator content into memory location 9050.

Instruction: STA 9050

Contents before instruction

Contents after instruction

A 9F XX F

9050 9F

#### 6. LDAX: Load Accumulator Indirect

| Opcode | Operand       | Bytes | Register Transfer Logic                               |

|--------|---------------|-------|-------------------------------------------------------|

| LDAX   | B/D Reg. pair | 1     | (A) $\leftarrow$ ((R <sub>h</sub> )(R <sub>l</sub> )) |

Description: The contents of the designated register pair point to a memory location. This instruction copies the content of that memory location into the accumulator. The contents of either the register pair or the memory location are not altered.

Flags: No flags are affected

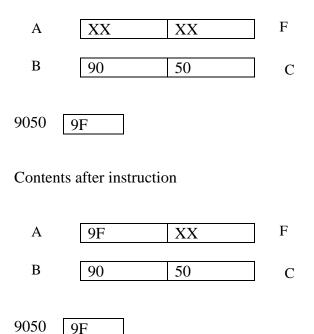

## Example :

Let us assume the contents of register B = 90, C = 50, and memory location 9050 = 9F. We want to transfer the contents of the memory location 9050 to the accumulator.

Instruction: LDAX B

Contents before instruction

#### 7. STAX: Store Accumulator Indirect

| Opcode | Operand       | Bytes | Register Transfer Logic                               |

|--------|---------------|-------|-------------------------------------------------------|

| LDAX   | B/D Reg. pair | 1     | (A) $\leftarrow$ ((R <sub>h</sub> )(R <sub>l</sub> )) |

Description: The contents of the accumulator are copied into the memory location specified by the contents of the operand (register pair). The contents of the accumulator are not altered.

Flags: No flags are affected

## Example :

Let us assume the contents of accumulator are F9 and the contents of B and C are 90 and 50 respectively. We want to store the accumulator contents in memory location 9050

Instruction: STAX B

Contents before instruction

[ Comments: This instruction performs the same function as MOV M, A except this instruction uses the contents of BC or DE as memory pointers.]

#### 8. LHLD: Load H and L Registers Direct

| Opcode | Operand        | Bytes | Register Transfer Logic      |

|--------|----------------|-------|------------------------------|

| LHLD   | 16-bit address | 3     | (L) ← (address)              |

|        |                |       | (H) $\leftarrow$ (address+1) |

Description: The instruction copies the contents of the memory location pointed out by the 16-bit address in register L and copies the contents of the next memory location.

Flags: No flags are affected

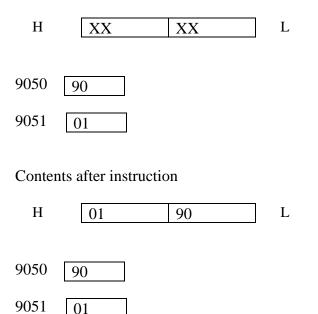

#### Example :

Let us assume memory location 9050 contains 90 and 9051 contains 01. Transfer of memory contents to register HL is to be performed.

Instruction: LHLD 9050

Contents before instruction

## 9. SHLD: Store H and L Registers Direct

| Opcode | Operand        | Bytes | Register Transfer Logic          |

|--------|----------------|-------|----------------------------------|

| SHLD   | 16-bit address | 3     | (address) ← (L)                  |

|        |                |       | $(address+1) \longleftarrow (H)$ |

Description: The contents of register L are stored in the memory location specified by the 16-bit address in the operand, and the contents of register H are stored in the next memory location by incrementing the operand. The contents of register HL are not altered. This is a 3-byte instruction; the second byte specifies the low-order address and the third byte specifies the high-order address.

Flags: No flags are affected

## Example :

Let us assume that the H and L registers contain 01 and FF respectively. We want to store the contents at memory locations 9050 and 9051.

Instruction: SHLD 9050

Contents before instruction

H 01 FF L

L

9050 XX

9051 XX

9051 XX

Contents after instruction

H 01 FF

9050 FF

9051 01

## 10. XCHG: Exchange H and L with D and E

| Opcode | Operand | Bytes | Register Transfer Logic |

|--------|---------|-------|-------------------------|

| XCHG   | -       | 1     | (H) ← (D)               |

|        |         |       | (L)                     |

Description: The contents of register H are exchanged with the contents of register D, and the contents of register L are exchanged with the contents of register E.

Flags: No flags are affected

## Example :

Let us assume that registers H and L contains the data bytes 98 and A4, respectively. Again, let us assume that registers D and E contains the data bytes C7 and 05, respectively.

Instruction: XCHG

Contents before instruction

| Н | 98 | A4 | L |

|---|----|----|---|

|   |    |    |   |

D C7 05 E

Contents after instruction

| Η | C7 | 05 | L |

|---|----|----|---|

|   |    |    |   |

D 98 A4 E

## 11. IN: Input Data to Accumulator from a Port with 8-bit Address

| Opcode | Operand              | Bytes | Register Transfer Logic         |

|--------|----------------------|-------|---------------------------------|

| IN     | <8-bit port address> | 2     | (A) $\leftarrow$ (port address) |

Description: The contents of the input port designated in the operand are read and loaded into the accumulator.

Flags: No flags are affected

[Comments: The operand is an 8-bit address; therefore, port addresses can range from 00 to FF. While executing the instruction, a port address is duplicated on low-order (A7-A0) and high-order (A15-A8) address buses. Any one of the sets of address lines can be decoded to enable the input port.]

## 12. OUT: Output Data from Accumulator to a Port with 8-bit Address

| Opcode | Operand              | Bytes | Register Transfer Logic         |

|--------|----------------------|-------|---------------------------------|

| OUT    | <8-bit port address> | 2     | (port address) $\leftarrow$ (A) |

Description: The contents of the accumulator are copied into the output port specified by the operand.

Flags: No flags are affected

[Comments: The operand is an 8-bit address; therefore, port addresses can range from 00 to FF. While executing the instruction, a port address is duplicated on low-order (A7-A0) and high-order (A15-A8) address buses. Any one of the sets of address lines can be decoded to enable the output port.]

#### **3.2.ARITHMETIC INSTRUCTION:**

The 8085 performs various arithmetic operations, such as addition, subtraction, increment and decrement. Arithmetic instructions perform these operations.

The instructions used to perform arithmetic operations are

- 1. ADD

- 2. ADI

- 3. ACI

- 4. ADC

- 5. SUB

- 6. SUI

- 7. SBB

- 8. SBI

- 9. INR

- 10. DCR

- 11. INX

- 12. DCX

- 13. DAD

- 14. DAA

#### 1. ADD: Add Register to Accumulator

| Opcode | Operand | Bytes | Register Transfer Logic         |

|--------|---------|-------|---------------------------------|

| ADD    | R       | 1     | (A) $\leftarrow$ (A) + (R)      |

| ADD    | М       | 1     | (A) $\leftarrow$ (A) + ((H)(L)) |

Description: The contents of the operand (register or memory) are added to the contents of the accumulator and the result is stored in the accumulator. If the operand is a memory location, that is indicated by the 16-bit address in the HL register

Flags: All flags are modified to reflect the result of the addition.

#### 2. ADI: Add Immediate to Accumulator

| Opcode | Operand    | Bytes | Register Transfer Logic              |

|--------|------------|-------|--------------------------------------|

| ADI    | 8-bit data | 2     | (A) $\leftarrow$ (A) + <data></data> |

Description: The 8-bit data are added to the contents of the accumulator and the result is stored in the accumulator.

Flags: All flags are modified to reflect the result of the addition.

## 3. ACI: Add Immediate to Accumulator with carry

| Opcode | Operand    | Bytes | Register Transfer Logic                   |

|--------|------------|-------|-------------------------------------------|

| ACI    | 8-bit data | 2     | (A) $\leftarrow$ (A) + CY + <data></data> |

Description: The 8-bit data (operand) and the carry flag are added to the contents of the accumulator, and the result is stored in the accumulator.

Flags: All flags are modified to reflect the result of the addition.

[Comments: This instruction is commonly used in 16-bit addition]

## 4. ADC: Add Register to Accumulator with carry

| Opcode | Operand | Bytes | Register Transfer Logic             |

|--------|---------|-------|-------------------------------------|

| ADC    | R       | 1     | $(A) \longleftarrow (A) + (R) + CY$ |

| ADC    | М       | 1     | (A) $\leftarrow$ (A) + ((H)(L) + CY |

Description: The contents of the operand (register or memory) and the carry flag are added to the contents of the accumulator and the result is placed in the accumulator. The contents of the operand are not altered, however, the previous carry flag is reset.

Flags: All flags are modified to reflect the result of the addition.

## Example :

Let us assume that register pair BC contains 2498 and register pair de contains 54A1. We add these 16-bit numbers and save the result in BC registers.

The steps in adding 16-bit numbers are as follows:

1. We add the contents of registers C and E by placing the contents of one register in the accumulator. This addition generates a carry. We use instruction ADD and save the low-order 8-bits in register C.

$\begin{array}{rrrr} 98 = & 10011000 \\ A1 = & 10100001 \end{array}$

1 39 = 1 00111001

We add the contents of registers B and D by placing the contents of one register in the accumulator. We use instruction ADC. The result will be as follows:

$\begin{array}{rcl} 24 = & 00100100 \\ 54 = & 01010100 \\ 1 & & 1 \mbox{ (Carry from previous addition)} \end{array}$

79 = 01111001 (We store in register B)

[Comments: This instruction is commonly used in 16-bit addition]

#### 5. SUB: Subtract Register or Memory from Accumulator

| Opcode | Operand | Bytes | Register Transfer Logic         |

|--------|---------|-------|---------------------------------|

| SUB    | R       | 1     | (A) $\leftarrow$ (A) – (R)      |

| SUB    | М       | 1     | (A) $\leftarrow$ (A) – ((H)(L)) |

Description: The contents of the register or the memory location specified by the operand are subtracted from the contents of the accumulator and the results are placed in the accumulator. The contents of the source are not altered.

Flags: All flags are modified to reflect the result of the subtraction.

#### Example 1:

Let us assume that the contents of the accumulator are 37 and the contents of the register C are 40. We subtract the contents of register C from the accumulator.

Instruction: SUB C

| (C) :          | 40       | = 01000000      |

|----------------|----------|-----------------|

| 2's complement | t of (C) | = 11000000      |

| (A) :          | 37       | = 00110111      |

|                |          | 0/11110111 = F7 |

| Complement ca  | urry:    | 1/11110111      |

Flags: S=1, Z=0, AC=0, P=0, CY=1

The result, as a negative number, will be in 2's complement and thus the Carry (Borrow) flag

is set.

#### Example 2:

Let us assume that the contents of the accumulator are 40 and the contents of the register C are 37. We subtract the contents of register C from the accumulator.

Instruction: SUB C

| (C) :<br>2's complement of | 37<br>(C) | $= 00110111 \\= 11001001$ |

|----------------------------|-----------|---------------------------|

| (A):                       | 40        | = 01000000                |

|                            |           | 0/00001001                |

| Complement carry:          |           | 0/00001001 = 09           |

Flags: S=0, Z=0, AC=0, P=1, CY=0

#### 6. SUI: Subtract Immediate from Accumulator

| Opcode | Operand    | Bytes | Register Transfer Logic              |

|--------|------------|-------|--------------------------------------|

| SUI    | 8-bit data | 2     | (A) $\leftarrow$ (A) – <data></data> |

Description: The 8-bit data are subtracted from the contents of the accumulator and the results are placed in the accumulator.

Flags: All flags are modified to reflect the result of the subtraction.

#### 7. SBB: Subtract Source and Borrow from Accumulator

| Opcode | Operand | Bytes | Register Transfer Logic             |

|--------|---------|-------|-------------------------------------|

| SBB    | R       | 1     | $(A) \leftarrow (A) - (R) - B$      |

| SBB    | М       | 1     | (A) $\leftarrow$ (A) - ((H)(L)) - B |

Description: The contents of the operand (register or memory) and the Borrow flag are subtracted from the contents of the accumulator and the results are placed in the accumulator.

#### Online Courseware for B.Tech. Computer Science and Engineering Program (Autonomy) Paper Name: Microprocessor and Microcontrollers Paper Code: CS602 Flags: All flags are modified to reflect the result of the subtraction.

#### 8. SBI: Subtract Immediate with Borrow

| Opcode | Operand    | Bytes | <b>Register Transfer Logic</b>      |

|--------|------------|-------|-------------------------------------|

| SBI    | 8-bit data | 2     | $(A) \longleftarrow (A) - data - B$ |

Description: The 8-bit data (operand) and the borrow are subtracted from the contents of the accumulator, and the results are placed in the accumulator.

Flags: All flags are modified to reflect the result of the operation.

#### 9. INR: Increment Contents of Register/Memory by 1

| Opcode | Operand | Bytes | Register Transfer Logic            |

|--------|---------|-------|------------------------------------|

| INR    | R       | 1     | $(R)  \bigstar  (R) + 1$           |

| INR    | М       | 1     | $((H)(L)) \leftarrow ((H)(L)) + 1$ |

Description: The contents of the designated register / memory are incremented by 1 and the results are stored in the same place. If the operand is a memory location, it is specified by the contents of HL register pair.

Flags: All flags except CY are modified to reflect the result of the operation.

#### Example 1:

Register D contains FF. we shall specify the contents of the register after the increment.

Instruction: INR D

(D): FF = 11111111

+1 = 00000001

$$0/0000000 = 00$$

After the execution of the INR instruction, register D will contain 00; however, carry flag is not modified.

#### Example 2:

We assume that the HL register contains 9075. We shall increment the contenmts of memory location 9075, which presently holds 7F.

#### Instruction: INR M

Contents before instruction

| Н       | 90             | 75     | L | 9075 | 7F |

|---------|----------------|--------|---|------|----|

| Content | ts after instr | uction |   |      |    |

| Н       | 90             | 75     | L | 9075 | 80 |

#### **10. DCR: Decrement Contents of Register/Memory by 1**

| Opcode | Operand | Bytes | Register Transfer Logic  |

|--------|---------|-------|--------------------------|

| DCR    | R       | 1     | $(R) \leftarrow (R) - 1$ |

| DCR    | М       | 1     | ((H)(L)) ← ((H)(L)) - 1  |

Description: The contents of the designated register / memory are decremented by 1 and the results are stored in the same place. If the operand is a memory location, it is specified by the contents of HL register pair.

Flags: All flags except CY are modified to reflect the result of the operation.

#### Example :

Register B contains 00. we shall specify the contents of the register after the decrement.

Instruction: DCR B

| +1                    |    | = | 00000 | 001      |

|-----------------------|----|---|-------|----------|

| 2's complement of 1's |    |   | =     | 11111111 |

| (B):                  | 00 |   | =     | 00000000 |

```

11111111 = FF

```

After the execution of the DCR instruction, register B will contain FF; however, carry flag is not

modified.

#### 11. INX: Increment Register Pair by 1

| Opcode | Operand   | Bytes | Register Transfer Logic                  |

|--------|-----------|-------|------------------------------------------|

| INX    | Reg. pair | 1     | (Reg. pair) $\leftarrow$ (Reg. pair) + 1 |

Description: The contents of the designated register pair are incremented by 1. The instruction views the contents of the two registers as a 16-bit number.

Flags: No flags are affected.

#### Example :

Register pair HL contains 9FFF. We shall specify the contents of the entire register if it is incremented by 1.

Instruction: INX H

After adding 1 to the contents of the HL pair the answer is (H) = A0, (L) = 00

Contents before instruction

H 9F FF L

Contents after instruction

H A0 00 L

#### 12. DCX: Decrement Register Pair by 1

| Opcode | Operand   | Bytes | Register Transfer Logic      |

|--------|-----------|-------|------------------------------|

| DCX    | Reg. pair | 1     | (Reg. pair) ← (Reg. pair) –1 |

Description: The contents of the designated register pair are decremented by 1. The instruction views the contents of the two registers as a 16-bit number.

Flags: No flags are affected.

#### Example :

Register pair DE contains 2000. We shall specify the contents of the entire register if it is decremented by 1.

Instruction: DCX D

After adding 1 to the contents of the HL pair the answer is (D) = 1F, (E) = FF

Contents before instruction

D 20 00 E

Contents after instruction

D 1F FF E

#### 13. DAD: Add Register Pair to H and I register pair

| Opcode | Operand   | Bytes | Register Transfer Logic              |

|--------|-----------|-------|--------------------------------------|

| DAD    | Reg. pair | 1     | (HL) $\leftarrow$ (Reg. pair) + (HL) |

Description: The 16-bit contents of the designated register pair are added to the contents of the HL register and the sum is saved in the HL register. The contents of the source register pair are not altered.

Flags: If the result is larger than 16 bits the CY flag is set. No other flags are affected

#### Example 1:

We assume that the register pair HL contains 0242. We want to multiply the contents by 2

Instruction: DAD H

Contents before instruction

H 02 42 L

DAD operation

$$\begin{array}{r} 0242 \\ + 0242 \\ \hline 0484 \end{array}$$

Contents after instruction

Η 04 84 L

#### **Example 2:**

We assume that the register pair HL is cleared. We want to transfer the content of Stack Pointer (SP) register that points to memory location FFFE to the HL register pair

Instruction: DAD SP

Contents before instruction

|   | п | 00 | 00 | L | SP | FFFE |

|---|---|----|----|---|----|------|

| · |   |    |    |   |    |      |

DAD operation

0000 + FFFE FFFE

Contents after instruction

Η

FF

FFFE

SP

#### 14. DAA: Decimal-Adjust Accumulator

FE

| Opcode | Operand | Bytes | Register Transfer Logic |

|--------|---------|-------|-------------------------|

| DAA    | -       | 1     |                         |

L

Description: The contents of the Accumulator are changed from a binary value to two binarycoded decimal (BCD) digits. This is the only instruction that uses the auxiliary flag (internally) to perform the binary-to-BCD conversion.

Flags: All flags are modified to reflect the result of the operation.

# **LECTURE 5: INSTRUCTION SET (LOGICAL INSTRUCTION)**

#### **3.3.LOGICAL INSTRUCTION:**

Logical Instructions:

These instructions perform various logical operations with the contents of the accumulator.

These instructions include:

ANA

ANI

ORA

- 4. ORI

- 5. XRA

- 6. XRI

- 7. CMA

- 8. CMP

- 9. CPI

- 10. RLC

- 11. RAL

- 12. RRC

- 13. RAR

- 14. STC

- 15. CMC

#### 1. ANA: Logical AND with Accumulator

| Opcode | Operand | Bytes | Register Transfer Logic           |

|--------|---------|-------|-----------------------------------|

| ANA    | R       | 1     | (A) $\leftarrow$ (A) AND (R)      |

| ANA    | М       | 1     | (A) $\leftarrow$ (A) AND ((H)(L)) |

Description: The contents of the Accumulator are logically ANDed with the contents of the operand (register or memory), and the result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of HL registers.

Flags: S, Z, P are modified to reflect the result of the operation. CY is reset. AC is set.

#### 2. ANI: AND Immediate with Accumulator

| Opcode | Operand      | Bytes | Register Transfer Logic                |

|--------|--------------|-------|----------------------------------------|

| ANI    | <8-bit data> | 2     | (A) $\leftarrow$ (A) AND <data></data> |

Description: The contents of the Accumulator are logically ANDed with the 8-bit data (operand)

and the result is placed in the accumulator.

Flags: S, Z, P are modified to reflect the result of the operation. CY is reset. AC is set.

#### 3. ORA: Logical OR with Accumulator

| Opcode | Operand | Bytes | Register Transfer Logic          |

|--------|---------|-------|----------------------------------|

| ORA    | R       | 1     | (A) $\leftarrow$ (A) OR (R)      |

| ORA    | М       | 1     | (A) $\leftarrow$ (A) OR ((H)(L)) |

Description: The contents of the Accumulator are logically ORed with the contents of the operand (register or memory), and the result is placed in the accumulator. If the operand is a memory location, its address is specified by the contents of HL registers.

Flags: S, Z, P are modified to reflect the result of the operation. CY and AC are reset.

#### 4. ORI: OR Immediate with Accumulator

| Opcode | Operand      | Bytes | Register Transfer Logic               |

|--------|--------------|-------|---------------------------------------|

| ANI    | <8-bit data> | 2     | (A) $\leftarrow$ (A) OR <data></data> |

Description: The contents of the Accumulator are logically ORed with the 8-bit data (operand) and the result is placed in the accumulator.

Flags: S, Z, P are modified to reflect the result of the operation. CY and AC are reset.

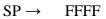

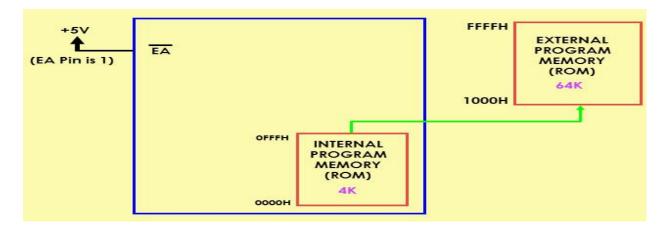

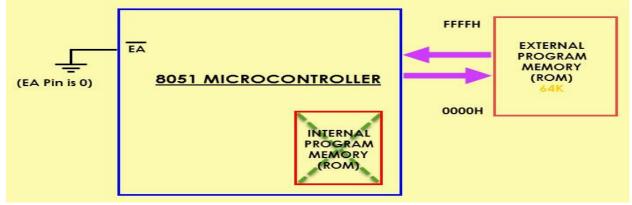

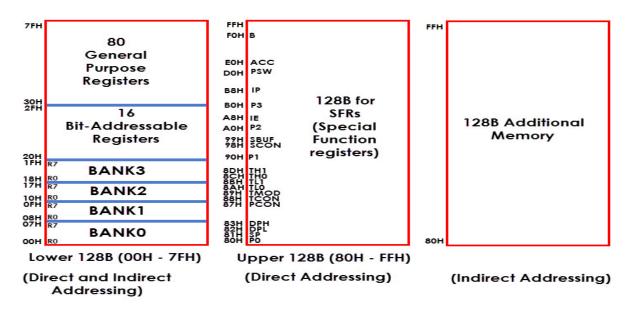

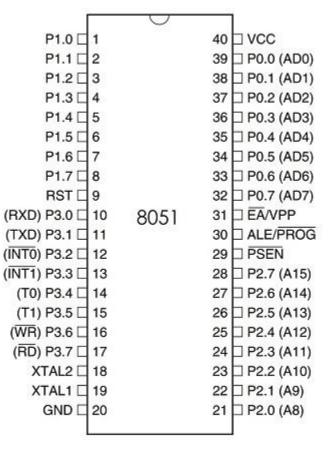

#### 5. XRA: Logical XOR with Accumulator