# Digital Electronic and Circuits EC403 Prepared by: Ms.Palasri Dhar, Mr. Shatadru Biswas

### MODULE I

#### Introduction:

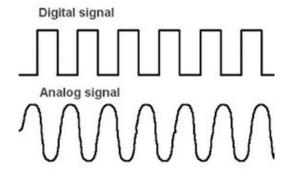

- Analog signals-The electrical signals that have any value over a rangeof time Example: A sinusoidal signal.

- Analog circuits-Circuits used to process the analog signals.

Example: Amplifier, filter etc.

• Digital signal-Electrical signals those have only two discrete values- high(1) and low(0).

Example: Binary data stream

• Digital circuits-Electronic circuitsthose process Digital signals. Example: Calculator

Figure 1 Picture of digital signal and analog signal

Introduction to Number System

Definition: Number system is the way to represent a number in different forms.

### Types of Number system:

- 1. Binary Number System: It is the number system with base value 2 means it has only two digits to represent the data. The digits are (0, 1). E.g. 00,01,10,11,100.

- 2. Decimal Number System: It is the number system with base value 10 means it has 10-digits to represent the data. The digits are(0-9). Eg. 0,1,2,3,4,5,6

- 3. Octal Number System: It is the number system with base value 8 means it has 8 digits to represent the data. The digits are (0-7).

- 4. Hexadecimal Number System: It is the number system with base value 16 means it has 16 digits to represent the data. The digits are (0-15). Eg. 0,1,2,3 .,9,A,B,C,D,E,F

### 1 The Binary Numbering System

We are habituated to use the decimal number system having the digits 0 to 9. This number system has a base of 10. But a computer or digital processor can recognize only binary 0 or 1. The Binary Numbering System is the most fundamental numbering system in all digital and computer based systems. It follow the same set of rules as the decimal numbering system. But unlike the decimal system which uses powers of ten, the binary numbering system works on powers of two giving a binary to decimal conversion from base-2 to base-10.

Digital logic and computer systems use just two values or states to represent a condition, a logic level 1 or a logic level 0, and each 0 and 1 is considered to be a single digit in a Base-of-2 (bi) or binary numbering system. In the binary numbering system, a binary number such as 101100101 is expressed with a string of 1 s and 0 s with each digit along the string from right to left having a value twice that of the previous digit. But as it is a binary digit it can only have a value of either 1 or 0 therefore, q is equal to 2 (0 or 1) with its position indicating its weight within the string. As the decimal number is a weighted number, converting from decimal to binary (base 10 to base 2) will also produce a weighted binary number with the right-hand most bit being the Least Significant Bit or LSB, and the left-hand most bit being the Most Significant Bit or MSB.

### 2 Representation of a Binary Number

| MSB | Binary Digit |                      |    |    |   |   | LSB |    |

|-----|--------------|----------------------|----|----|---|---|-----|----|

| 28  | 27           | 27 26 25 24 23 22 21 |    |    |   |   |     | 20 |

| 256 | 128          | 64                   | 32 | 16 | 8 | 4 | 2   | 1  |

3 Binary Number Names & Prefixes

The classification of individual bits into larger groups is generally referred to by the following more common names of:

| Number of Binary Digits (bits) | Common Name |

|--------------------------------|-------------|

| 1                              | Bit         |

| 4                              | Nibble      |

| 8                              | Byte        |

| 16                             | Word        |

| 32                             | Double Word |

| 64                             | Quad Word   |

### 4 Conversion from Binary to Decimal

# Conversion of Integer Numbers

Expand the number given in binary form in the power of 2 and sum the values, the result which we will get will be in the decimal form. For example-

get will be in the decimal form. For example-

$$(1110)_2=1\times 2^3+1\times 2^2+1\times 2^1+0\times 2^0=(15)_{10}$$

Conversion of Decimal Point Number to Decimal

This can also be done in the same way, however after the decimal point the number should be multiplied with  $2^{-1}$ ,  $2^{-2}$  etc. For example,

$$\begin{array}{l} \text{(1110.011)}_2 = 1 \times 2^3 + 1 \times 2^2 + 1 \times 2^1 + 0 \times 2^0 + 0 \times 2^{-1} + 1 \times 2^{-2} + 1 \times 2^{-3} \\ = (15.375)_{10} \end{array}$$

### 5 Conversion from Decimal to Binary

### Integer Numbers

Divide the number by 2 and take only the remainder, if division is completed than take only the remainder which gives the binary number.

Suppose we are converting the decimal number  $(87)^{10}$ . Now the conversion is shown below.

$$\begin{array}{c|cccc}

2 & 87 & \longrightarrow & 1 \\

2 & 43 & \longrightarrow & 1 \\

2 & 21 & \longrightarrow & 1 \\

2 & 10 & \longrightarrow & 0 \\

2 & 5 & \longrightarrow & 1 \\

2 & 2 & \longrightarrow & 0 \\

\hline

1 & & & & & \\

\end{array}$$

$$(87)_{10} = (1110101)_2$$

#### For Fractional Numbers

In this case, the successive multiplication is done. The number which is to be converted is multiplied with base or radix of binary number which is 2. The integer part or the carry of the product is taken out and the same process is repeated until we get an integer. For example- The binary equivalent of

$$.95 \times 2 = 1.90 - - - - - - 1 \text{ is taken out} \\ .90 \times 2 = 1.80 - - - - - - 1 \\ .80 \times 2 = 1.60 - - - - - - 1 \\ .60 \times 2 = 1.20 - - - - - - - - 1 \\ .20 \times 2 = .40 - - - - - - - - - - - - 1 \\ .20 \times 2 = .40 - - - - - - - - - - - - - - - 1 \\ (.95)_{10} \text{ is evaluated as } .40 \times 2 = .80 - - - - - - - - - - - - - 0 \\ \text{follows.}$$

Since, we are not getting the integer value after successive multiplication, we can approximate the value to be (.111110.)<sub>2</sub>.

#### 6 Conversion from Octal to decimal

A regular decimal number is the sum of the digits multiplied with 10<sup>n</sup>.

Example #1

137 in base 10 is equal to each digit multiplied with its corresponding 10<sup>n</sup>:

$$137_{10} = 1 \times 10^2 + 3 \times 10^1 + 7 \times 10^0 = 100 + 30 + 7$$

Octal numbers are read the same way, but each digit counts 8<sup>n</sup> instead of 10<sup>n</sup>. Multiply each digit of the hex number with its corresponding 8<sup>n</sup>.

### 7 Conversion from Octal to Binary

Converting from octal to binary is as easy as converting from binary to octal. Simply look up each octal digit to obtain the equivalent group of three binary digits.

| Octal:  | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   |

|---------|-----|-----|-----|-----|-----|-----|-----|-----|

| Binary: | 000 | 001 | 010 | 011 | 100 | 101 | 110 | 111 |

$Octal = 3 \quad 4 \quad 5$

Binary = 011 100 101 = 011100101 binary

#### 8 Conversion fromOctal to Hexadecimal

When converting from octal to hexadecimal, it is often easier to first convert the octal number into binary and then from binary into hexadecimal. For example, to convert 345 octal into hex:

(from the previous example)

$Octal = 3 \quad 4 \quad 5$

Binary =  $011\ 100\ 101 = 011100101$  binary

| Binary:      | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 |

|--------------|------|------|------|------|------|------|------|------|

| Hexadecimal: | 0    | 1    | 2    | 3    | 4    | 5    | 6    | 7    |

| Binary:      | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| Hexadecimal: | 8    | 9    | A    | В    | C    | D    | Е    | F    |

### 9 Conversion from Hexadecimal to decimal

A regular decimal number is the sum of the digits multiplied with 10<sup>n</sup>.

### Example #1

137 in base 10 is equal to each digit multiplied with its corresponding 10<sup>n</sup>:

$$137_{10} = 1 \times 10^2 + 3 \times 10^1 + 7 \times 10^0 = 100 + 30 + 7$$

Hex numbers are read the same way, but each digit counts 16<sup>n</sup> instead of 10<sup>n</sup>. Multiply each digit of the hex number with its corresponding 16<sup>n</sup>.

### Example #2

3B in base 16 is equal to each digit multiplied with its corresponding 16<sup>n</sup>:

$$3B_{16} = 3 \times 16^{1} + 11 \times 16^{0} = 48 + 11 = 59$$

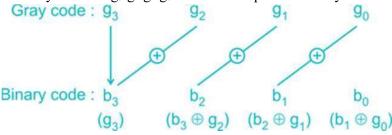

### 10 Conversion from Gray Code to Binary Code

Let Gray Code be  $g_3$   $g_2$   $g_1$   $g_0$ . Then the respective Binary Code can be obtained as follows:

i.e.

$$b_3 = g_3 b_2 =$$

$$b_3 \square g_2 b_1 =$$

$$b_2 \square g_1$$

$$b_0 = b_1 \square g_0$$

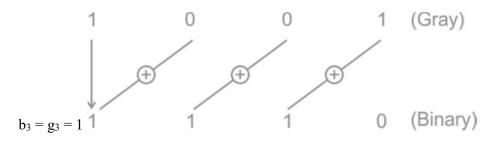

Example:

Gray Code:  $g_3$   $g_2$   $g_1$   $g_0 = 1$  0 0 1 then Binary Code:  $b_3$   $b_2$   $b_1$   $b_0$

$$b_2 = b_3 \square \ g_2 = 1 \square \ 0 = 1$$

$$b_1 = b_2 \square \ g_1 = 1 \ \square \ 0 = 1$$

$$b_0 = b_1 \square \ g_0 = 1 \ \square \ 1 = 0$$

: Final Binary Code: 1 1 1 0

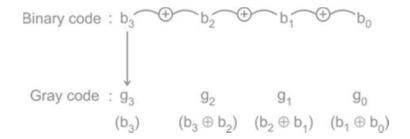

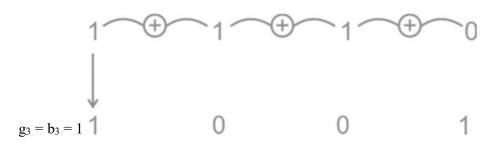

### 11 Conversion from Binary code to Gray Code

Let Binary code be b<sub>3</sub> b<sub>2</sub> b<sub>1</sub> b<sub>0</sub>. Then the respective Gray Code can be obtained is as follows

i.e.

$$g_3 = b_3 g_2 =$$

$$b_3 \square \ b_2 \ g_1 =$$

$$b_2 \square \ b_1 \ g_0 =$$

$$b_1 \square \ b_0$$

## Example:

Binary Code:  $b_3 b_2 b_1 b_0 = 1 1 1 0$  Gray Code:  $g_3 g_2 g_1 g_0$

$$g_2 = b_3 \Box \ b_2 = 1 \ \Box \ 1 = 0$$

$$g_1 = b_2 \square \ b_1 = 1 \ \square \ 1 = 0$$

$$g_0 = b_1 \square \ b_0 = 1 \ \square \ 0 = 1$$

: Final Gray code: 1 0 0 1

### 12 Conversion Table from Binary to Gray Code:

| Decimal | Binary | Gray |

|---------|--------|------|

| 0       | 0000   | 0000 |

| 0001 | 0001                                                                                                 |

|------|------------------------------------------------------------------------------------------------------|

| 0010 | 0011                                                                                                 |

| 0011 | 0010                                                                                                 |

| 0100 | 0110                                                                                                 |

| 0101 | 0111                                                                                                 |

| 0110 | 0101                                                                                                 |

| 0111 | 0100                                                                                                 |

| 1000 | 1100                                                                                                 |

| 1001 | 1101                                                                                                 |

| 1010 | 1111                                                                                                 |

| 1011 | 1110                                                                                                 |

| 1100 | 1010                                                                                                 |

| 1101 | 1011                                                                                                 |

| 1110 | 1001                                                                                                 |

| 1111 | 1000                                                                                                 |

|      | 0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001<br>1010<br>1011<br>1100<br>1101<br>1110 |

## Binary Coded Decimal:

BCD or Binary Coded Decimal is that number system or code which has the binary numbers or digits to represent a decimal number. A decimal number contains 10 digits (0-9). Now the equivalent binary numbers can be found out of these 10 decimal numbers. In case of BCD the binary number formed by four binary digits, will be the equivalent code for the given decimal digits. In BCD we can use the binary number from 0000-1001 only, which are the decimal equivalent from 0-9 respectively. It is also called 8421 code.

Binary Coded Decimal Representation of a Decimal Number

| Binary Power   | $2^3$ | 22 | 21 | 20 |

|----------------|-------|----|----|----|

| Binary Weight: | 8     | 4  | 2  | 1  |

The decimal weight of each decimal digit to the left increases by a factor of 10. In the BCD number system, the binary weight of each digit increases by a factor of 2 as shown. Then the first digit has a weight of 1 ( $2^0$ ), the second digit has a weight of 2 ( $2^1$ ), the third a weight of 4 ( $2^2$ ), the fourth a weight of 8 ( $2^3$ ).

Then the relationship between decimal (denary) numbers and weighted binary coded decimal digits is given below.

Truth Table for Binary Coded Decimal

| Decimal Number | BCD 8421 Code |

|----------------|---------------|

| 0              | 0000 0000     |

| 1              | 0000 0001     |

| 2              | 0000 0010     |

| 3              | 0000 0011     |

| 4              | 0000 0100     |

| 5              | 0000 0101     |

| 6              | 0000 0110     |

| 7              | 0000 0111     |

| 8              | 0000 1000     |

| 9              | 0000 1001     |

| 10 (1+0)       | 0001 0000     |

| 11 (1+1)       | 0001 0001     |

| 12 (1+2)       | 0001 0010     |

|                |               |

| 20 (2+0)       | 0010 0000     |

| 21 (2+1)       | 0010 0001     |

| 22 (2+2)                                  | 0010 0010 |  |  |

|-------------------------------------------|-----------|--|--|

| etc, continuing upwards in groups of four |           |  |  |

Then we can see that 8421 BCD code is nothing more than the weights of each binary digit, with each decimal (denary) number expressed as its four-bit pure binary equivalent.

#### Decimal-to-BCD Conversion

As we have seen above, the conversion of decimal to binary coded decimal is very similar to the conversion of hexadecimal to binary. Firstly, separate the decimal number into its weighted digits and then write down the equivalent 4-bit 8421 BCD code representing each decimal digit as shown.

### Binary Coded Decimal Example No1

Using the above table, convert the following decimal (denary) numbers: 85<sub>10</sub>, 572<sub>10</sub> and 8579<sub>10</sub> into their 8421 BCD equivalents.

```

85<sub>10</sub> = 1000 0101 (BCD)

572<sub>10</sub> = 0101 0111 0010 (BCD)

8579<sub>10</sub> = 1000 0101 0111 1001 (BCD)

```

Note that the resulting binary number after the conversion will be a true binary translation of decimal digits. This is because the binary code translates as a true binary count.

#### BCD-to-Decimal Conversion

The conversion from binary coded decimal to decimal is the exact opposite of the above. Simply divide the binary number into groups of four digits, starting with the least significant digit and then write the decimal digit represented by each 4-bit group. Add additional zero s at the end if required to produce a complete 4-bit grouping. So for example,  $110101_2$  would become:  $0011\ 0101_2$  or  $35_{10}$  in decimal.

Convert the following binary numbers: 1001<sub>2</sub>, 1010<sub>2</sub>, 1000111<sub>2</sub> and 10100111000.101<sub>2</sub> into their decimal equivalents.

```

1001_2 = 1001_{BCD} = 9_{10}

```

$1010_2$  = this will produce an error as it is decimal  $10_{10}$  and not a valid BCD number

```

1000111_2 = 0100 \ 0111_{BCD} = 47_{10}

```

$10100111000.101_2 = 0101\ 0011\ 0001.1010_{BCD} = 538.625_{10}$

ASCII:

ASCII stands for American Standard Code for Information Interchange. Computers can only understand numbers, so an ASCII code is the numerical representation of a character such as 'a' or '@' or an action of some sort. ASCII was developed a long time ago and now the non-printing characters are rarely used for their original purpose. Below is the ASCII character table and this includes descriptions of the first 32 non-printing characters. ASCII was actually designed for use with teletypes and so the descriptions

are somewhat obscure. If someone says they want your CV however in ASCII format, all this means is they want 'plain' text with no formatting such as tabs, bold or underscoring - the raw format that any computer can understand. This is usually so they can easily import the file into their own applications without issues. Notepad.exe creates ASCII text, or in MS Word you can save a file as 'text only'

ASCII was developed by the American National Standards Institute (ANSI). In an ASCII file, each alphabetic, numeric, or special character is represented with a 7-bit binary number (a string of seven 0s or 1s). 128 possible characters are defined.

UNIX and DOS-based operating systems use ASCII for text files. Windows NT and 2000 uses a newer code, Unicode. IBM's S/390 systems use a proprietary 8-bit code called EBCDIC. Conversion programs allow different operating systems to change a file from one code to another.

EBCDIC:(Extended Binary Coded Decimal Interchange Code)

EBCDIC is a <u>binary</u> code for alphabetic and numeric characters that IBM developed for its larger operating systems. It is the code for text files that is used in IBM's OS/390 operating system for its S/390 servers and that thousands of corporations use for their <u>legacy applications</u> and <u>databases</u>. In an EBCDIC file, each alphabetic or numeric character is represented with an 8-bit binary number (a string of eight 0's or 1's). 256 possible characters (letters of the alphabet, numerals, and special characters) are defined.

IBM's PC and workstation operating systems do not use IBM's proprietary EBCDIC. Instead, they use the industry standard code for text, ASCII. Conversion programs allow different operating systems to change a file from one code to another.

### ONE S COMPLEMENT AND TWO S COMPLEMENT

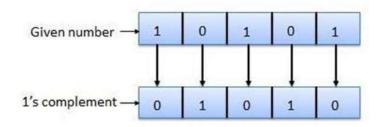

#### 13 One's complement

The 1's complement of a number is found by changing all 1's to 0's and all 0's to 1's. This is called as taking complement or 1's complement. Example of 1's Complement is as follows.

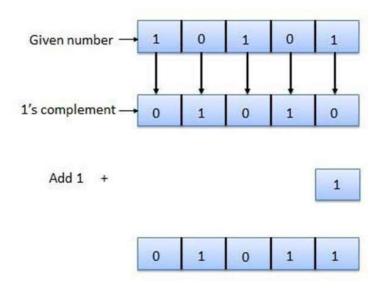

### 14 Two's complement

The 2's complement of binary number is obtained by adding 1 to the Least Significant Bit (LSB) of 1's complement of the number.

2's complement = 1's complement + 1 Example of 2's Complement is as follows.

### 9 s and 10 s complement methods:

The complements are used to make the arithmetic operations in digital system easier. In this article we will discuss about the following topics

- 1. 9s complement

- 2. 10s complement

- 3. 9s complement subtraction

- 4. 10s complement subtraction

Now first of all let us know what 9's complement is and how it is done.

To obtain the 9's complement of any number we have to subtract the number with  $(10^n - 1)$  where n = number of digits in the number, or in a simpler manner we have to divide each digit of the given decimal number with 9. The table given below will explain the 9's complement more easily.

| Decimal digit | 9s complement |

|---------------|---------------|

| 0             | 9             |

| 1             | 8             |

| 2             | 7             |

| 3             | 6             |

| 4             | 5             |

| 5             | 4             |

| 6             | 3             |

| 7             | 2             |

| 8             | 1             |

| 9             | 0             |

### Now coming to 10's complement

it is relatively easy to find out the 10's complement after finding out the 9,s complement of that number. We have to add 1 with the 9's complement of any number to obtain the desired 10's complement of that number. Or if we want to find out the 10's complement directly, we can do it by following the following formula,  $(10^n - number)$ , where n = number of digits in the number. An example is given below to illustrate the concept of obtaining 10 s complement

Let us take a decimal number 456, 9's complement of this number will be

10's complement of this no.

9's complement subtraction:

We will understand this method of subtraction via an example

A = 215

B = 155

We want to find out A-B by 9's complement subtraction method

First we have to find out 9 s complement of B

999

155 (-)

844

Now we have to add 9 s complement of B to A

844

215(+)

1059

The left most bit of the result is called carry and is added back to the part of the result without it

059

1(+)

60

Another different type of example is given

A = 4567

B = 1234

We need to find out A - B 9's complement of B 8765 Adding 9's complement of B with A 8765 4567 13332 Adding the carry with the result we get 3333 Now the answer is - 3333 NB if there is no carry the answer will be (9 s complement of the answer) Subtraction by 10's complement: Again we will show the procedure by an example Taking the same data A = 215B = 15510's complement of B = 845Adding 10 s complement of B to A 845 215 (+) 1060 In this carry omitted case the is is 60 The answer 15 Representation of Negative Number In case of a negative number we can go for 2 scomplement representation of a signed number. Example- $9 = 0000 \ 1001 \ 1 \ s$  complement = 1111 0110. Adding 1 we get = 11110111 which is the 2 s complement

representation of (-9).

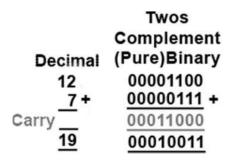

2.4 Two s Complement Addition: An example of addition using 8 bit twos complement notation. When adding two positive numbers, the sign bit (msb) will both be 0, so the numbers are written and added as a pure 8-bit binary addition

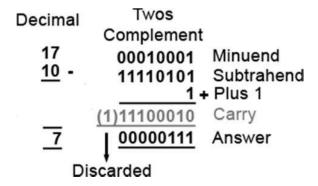

16 Two s Complement Subtraction

One positive number (the subtrahend) is subtracted from a larger positive number (the minuend). In this case the minuend is  $17_{10}$  and the subtrahend is  $10_{10}$ .

When these three lines of digits, and any carry 1 bits are added, remembering that in twos complement, any carry from the most significant bit is discarded.

#### Case1:

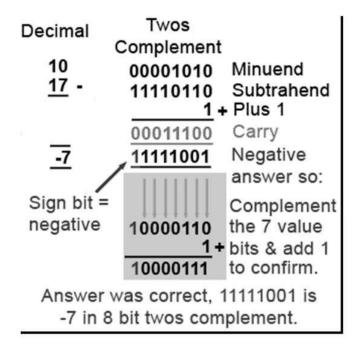

Some subtractions will of course produce an answer with a negative value. In Fig. below the result of subtracting 17 from 10 should  $-7_{10}$  but the twos complement answer of  $11111001_2$  certainly doesn't look like -7. However the sign bit is indicating correctly that the answer is negative, so in this case the 7 bits indicating the value of the negative answer need to be 'twos complemented' once more to see the answer in a recognizable form.

#### Case2:

17

#### **BOOLEANLAWS**

There are different types of Boolean Laws as follows.

#### AND law

These laws use the AND operation. Therefore they are called as AND laws.

(i)

$$A.0 = 0$$

(ii)

$$A.1 = A$$

#### OR law

These laws use the OR operation. Therefore they are called as **OR** laws.

(i)

$$A + 0 = A$$

(ii)

$$A + 1 = 1$$

(iii)

$$A + A = A$$

#### **INVERSION law**

This law uses the NOT operation. The inversion law states that double inversion of variable results in the original variable itself.

$$\overline{\overline{A}} = A$$

#### Commutative law

Any binary operation which satisfies the following expression is referred to as commutative operation.

(i)

$$A.B = B.A$$

(ii)  $A + B = B + A$

Commutative law states that changing the sequence of the variables does not have any effect on the output of a logic circuit.

Associative law

This law states that the order in which the logic operations are performed is irrelevant as their effect is the same.

(i)

$$(A.B).C = A.(B.C)$$

(ii)  $(A+B)+C=A+(B+C)$

Distributive law

This law is composed of two operators, AND and OR.

$$A.(B+C) = A.B + A.C$$

Let us show one use of this law to prove the expression

Proof:

$$A + B.C = (A + B). (A + C)$$

$A + B.C = A.1 + B.C [Since, A.1 = A]$

$= A. (1 + B) + B.C [Since, B + 1 = 1]$

$= A.1 + AB + BC$

$= A. (1 + C) + AB + BC [Since, A.A = A.1 = A]$

$= A. (A + C) + B. (A + C)$

$= (A + B). (A + C)$

(a)

$$A (B + C) = A B + A C$$

(b)  $A + (B C) = (A + B) (A + C)$

now proof for 1st no. is as simple as we can see

$$=AB+BC$$

$$=A(B+C) L.H.S=R.H.S.$$

now proof for 2nd. law R.H.S. = (A+B)(A+C)

Redundant Literal Rule

L.H.S. = R.H.S.

$$AA + \overline{AA} + AB + \overline{AB}$$

$$A + \overline{A}B = A + B$$

Similarly,

From truth table it is proved that,  $A(\overline{A} + B) = AB$

Associative Laws for Boolean Algebra

This law is for several variables, where the OR operation of the variables result is same though the grouping of the variables. This law is quite same in case of AND operators.

$$(A + B) + C = A + (B + C)$$

$(A. B). C = A. (B. C)$

Absorption Laws for Boolean Algebra

$$A + A.B = A$$

$A + A.B = A(1 + B) = A$

$Similarly, A(A + B) = A$

18 De-Morgan's Theorem

Theorem 1: The compliment of the product of two variables is equal to the sum of the compliment of each variable. Thus according to De-Morgan's laws or De-Morgan's theorem if A and B are the two variables or Boolean numbers. Then accordingly

$$\overline{A} + \overline{B} = \overline{A} \ \overline{B}$$

and  $\overline{AB} = \overline{A} + \overline{B}$

Theorem 2: The compliment of the sum of two variables is equal to the product of the compliment of each variable. Thus according to De Morgan s theorem if A and B are the two variables then.

$$(A+B)'=A'.B'$$

7.16 Examples of Boolean algebra

Simplify,

$$(A + \overline{B})(C + \overline{D})$$

Here,

$$(A + \overline{B})(C + \overline{D})$$

[ As per De Morgan Therem  $\overline{x}.\overline{y} = \overline{x} + \overline{y}$  ]

$$= \overline{(A + \overline{B})(C + \overline{D})} [ As per De Morgan Therem \overline{x + y} = \overline{x}.\overline{y} ]$$

$$= \overline{A}.\overline{B} + \overline{C}.\overline{D}$$

$$= \overline{A}B + \overline{C}D$$

1. Another example,

$$\overline{AB} + \overline{A} + AB = \overline{AB}. \overline{A}. \overline{AB}$$

[Appling De Morgan Therem]

=  $AB. A. \overline{AB}$

=  $AB. \overline{AB}. A = 0$

Example simplify,

$$AB + A\overline{B}C + B\overline{C} = A(B + \overline{B}C) + B\overline{C} = A(B + \overline{B})(B + C) + B\overline{C}$$

$$= AB + AC + B\overline{C} = AB(C + \overline{C}) + AC + B\overline{C} = ABC + AB\overline{C} + AC + B\overline{C}$$

$$= AC(1 + B) + B\overline{C}(A + 1) = AC + B\overline{C}$$

Minimization of logic expressions by algebraic method:

Some examples:

1.

$$(A + B)(A + C) = AA + AC + AB + BC$$

$$= A + AC + AB + BC$$

$$= A(1 + C + B) + BC$$

$$= A \cdot 1 + BC$$

$$= A + BC$$

2.

$$(\overline{A} + B)(A + B) = B(\overline{A} + A)$$

$$B(1)$$

$$B$$

$$A\overline{C} + AB\overline{C} = A\overline{C} (1 + B)$$

$$A\overline{C} (1)$$

$$A\overline{C}$$

4.

$$A\overline{B}D + A\overline{B}\overline{D} = A\overline{B}(D + \overline{D})$$

$$A\overline{B}(1)$$

$$A\overline{B}$$

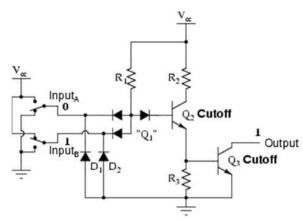

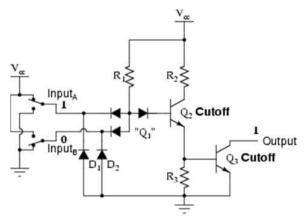

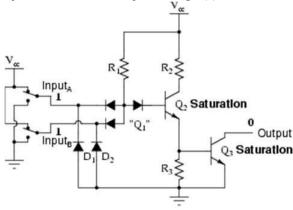

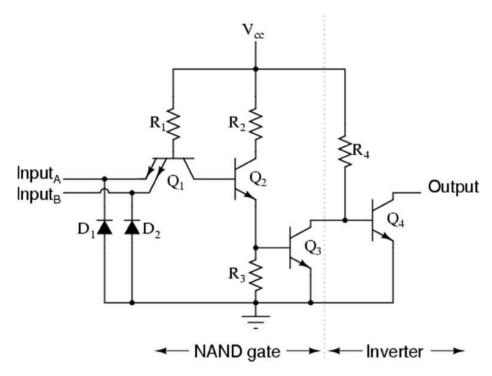

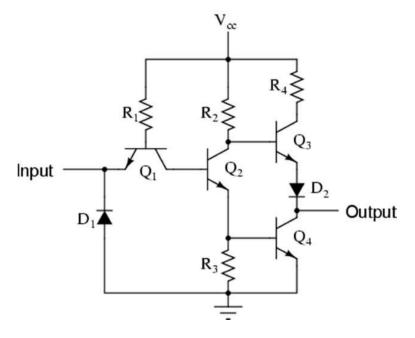

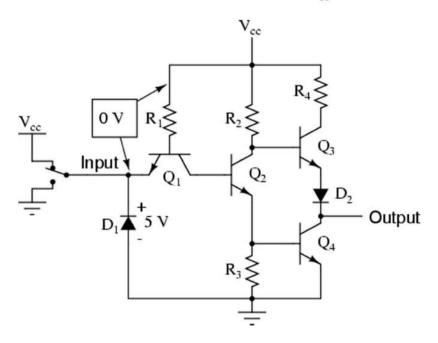

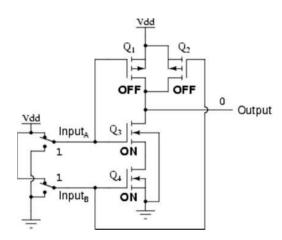

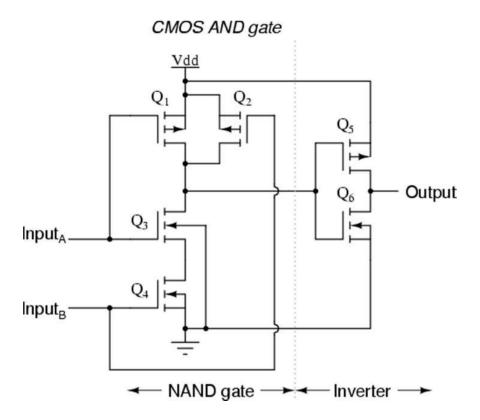

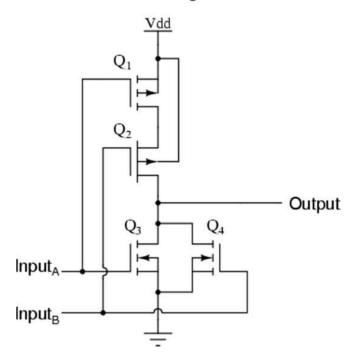

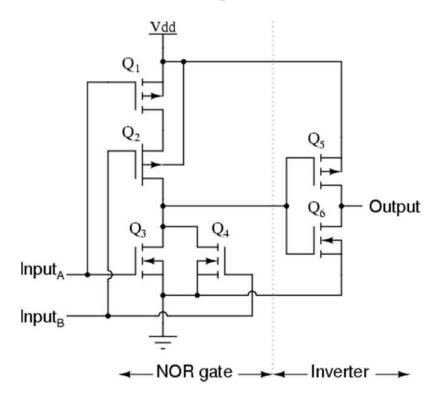

$A \ \overline{B}$  LOGIC GATES- Transistor or IC circuits produce digital output for given digital inputs following some logical operations.

| Name | Graphical Symbol | Algebraic<br>Function          | Truth Table                               |

|------|------------------|--------------------------------|-------------------------------------------|

| AND  | A F              | $F = A \cdot B$ or $F = AB$    | A B F<br>0 0 0<br>0 1 0<br>1 0 0<br>1 1 1 |

| OR   | A F              | F = A + B                      | A B F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 1 |

| NOT  | A — F            | $F = \overline{A}$ or $F = A'$ | A F<br>0 1<br>1 0                         |

| NAND | А F              | $F = \overline{AB}$            | A B F<br>0 0 1<br>0 1 1<br>1 0 1<br>1 1 0 |

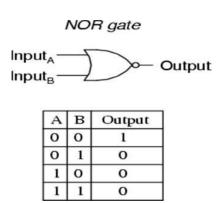

| NOR  | A B              | $F = \overline{A + B}$         | A B F<br>0 0 1<br>0 1 0<br>1 0 0<br>1 1 0 |

| XOR  | A B              | $F = A \oplus B$               | A B F<br>0 0 0<br>0 1 1<br>1 0 1<br>1 1 0 |

BASIC GATES- AND, OR, NOT

Any basic gates can be implemented using these two universal gates using some logic operations.

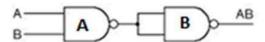

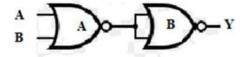

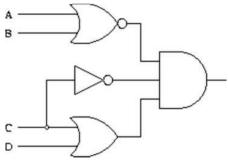

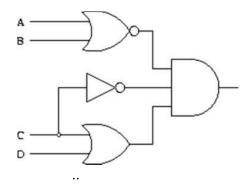

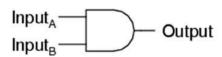

(a) Implementation of AND gate using NAND gate:

For a 2-input (A,B), AND gate has the Boolean function as Y= A.B

It can be written as  $Y = \overline{A.B}$

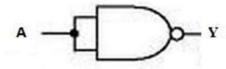

## (b) Implementation of NOT gate using NAND gate:

For a 2-input (A,B),NOT gate has the Boolean function as  $F = \overline{A}$ . It can be written as  $F = \overline{A \cdot A}$

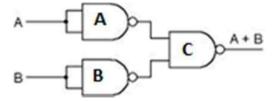

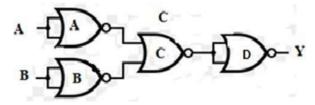

### (c) Implementation of OR gate using NAND gate:

For a 2-input (A,B), OR gate has the Boolean function as Y = A + B.

It can be written as  $Y = \overline{A + B}$

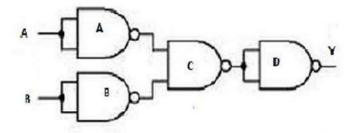

### (d) Implementation of NOR gate using NAND gate:

For a 2-input (A, B), OR gate has the Boolean function as  $Y = \overline{A + B}$ . It can be written as  $Y = \overline{A \cdot B} = \overline{A \cdot B} = \overline{A + B}$

(e) Implementation of NOR gate using NAND gate:

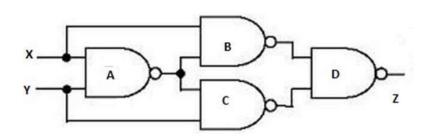

(f) Implementation of AND gate using NOR gate:

For a 2 input (A,B), AND gate has the Boolean function as Y = A.B. It can be written as  $Y = \overline{A.B}$

(g) Implementation of NOT gate using NOR gate:

For a 2-input (A,B),NOT gate has the Boolean function as  $F = \overline{A}$

It can be written as  $F = \overline{A.A}$

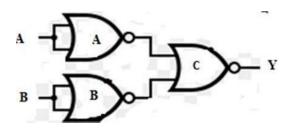

(h) Implementation of OR gate using NOR gate:

For a 2-input (A,B), OR gate has the Boolean function as Y= A+B

It can be written as  $Y = \overline{A + B}$

(i) Implementation of NAND gate using NOR gate:

For a 2-input (A,B), OR gate has the Boolean function as  $Y = \overline{A \cdot B}$  It can be written as  $Y = \overline{A \cdot B} = \overline{A \cdot B} = \overline{A \cdot B}$

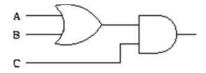

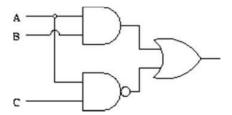

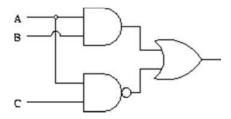

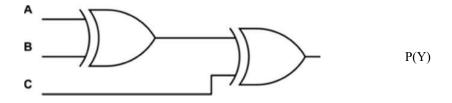

• Draw a logic circuit for (A + B)C.

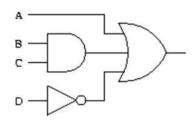

• Draw a logic circuit for A + BC + D.

• Draw a logic circuit for AB + AC.

• Draw a logic circuit for (A + B)(C + D)C.

SOLVED PROBLEMS

1. Simplify AB + ABC + BC

$$AB + A\overline{B}C + B\overline{C} = A(B + \overline{B}C) + B\overline{C} = A(B + \overline{B})(B + C) + B\overline{C}$$

$$= AB + AC + B\overline{C} = AB(C + \overline{C}) + AC + B\overline{C} = ABC + AB\overline{C} + AC + B\overline{C}$$

$$= AC(1 + B) + B\overline{C}(A + 1) = AC + B\overline{C}$$

2. Draw a logic circuit for (A + B)C.

3. Draw a logic circuit for A + BC + D.

4. Draw a logic circuit for AB + AC.

5. Draw a logic circuit for (A + B) (C + D) C.

MCQ

1. Given that  $(\sqrt{61})_b$  = 7<sub>10</sub>, the value of b is

A. 6 B. 8 C. 4

D. 5

Ans. B

Subtraction of two signed numbers is performed with

1's complement

- A. 2's complement

- B. 9's complement

- C. 10's complement

Ans. B

- 2. Representation of 8620 in binary is

- A. 1000 0111 1110 0000

- B. 1000\_0110\_0010\_0000

- C. 1000\_0110\_1010\_0000

- D. 1011\_0110\_0010\_0000

- 3. -9 with signed 2's complement representation is

- A. 10001001

- B. 11110110

- C. 11110111

- D. 11110011

Ans. C

- 4. NOT gate is also known as

- A. Converter

- B. Inverter

- C. Complementer

- D. Both b and c

Ans. D

- 5.  $(72.45)_{10} = (?)_2$

- A. 100100.01110

- B. 110000.00111

- C. 100100.1110

- D. 111000.01110

Ans. A

- 6.  $(381B)_{16}=(?)_8$

- A. 33033

- B. 34033

- C. 30334

- D. 33004

Ans. B

- 7.  $(49)_{16} = (?)_2$

- A. 10001111

- B. 1110 0010

- C. 01001011

- D. 01011011

Ans. C

8.

$$(137)_8 = (?)_{16}$$

- A. 5F

- B. 5B

- C. F5

- D. 59 Ans. A

9.

$$(632)_{16}=(?)_{10}$$

- A. 1587

- B. 1588

- C. 1557

- D. 1586

Ans.D

.....

### Answer The Following Questions:

$$\overline{(A+\overline{B})(C+\overline{D})}$$

$$\overline{AB}+\overline{A}+AB=\overline{AB}.\overline{A}.\overline{AB}$$

Simplify

- 2. Prove that,

- 3. Implement the Boolean function, (A + B) C using universal gate only.

- 4. State DeMorgan s theorem.

- 5. State and prove Absorption, Associative and Distributive law.

- 6. Using Boolean algebra, verify

$$(A+B)(B+C)(C+A)=AB+BC+CA$$

- 7. Explain the term Universal Logic gate

- 8. Explain how the basic gates are realised using NAND gate.

- 9. Explain how the basic gates are realised using NOR gate..

- 10. Write the truth table of XOR gate and construct it with NAND gate.

.....

#### Solve the problems

1. Convert the following decimal number to binary equivalent:

4097.18

2. Convert the following binary number to octal and then hexadecimal:

1011101.1011

3. Simplify the following Boolean function:

(A+B)(A'+C)

ANS:

- 1.100000000001.001,

- 2. 135.54, 5D.B

- 3. AC+A'B+BC

#### Sum of Products & Product of Sums

All Boolean expressions can be converted into one of two standard forms; the sum-of-product form and the product-of sum forms.

The Sum-of-Product (SOP):

SOP form means that the inputs of each term are multiplied using AND function, then all terms are added together using OR function. The variables in each term are not necessarily all the variables of the function. For example, a SOP of F(A,B,C) may contain a term that contains only the variable A but not B nor C, in such case the term is not in its standard SOP form. Standard SOP term must contain all the function variables. From Boolean algebra thermos (X+X'=1), then if the term is multiplied by (X+X'), it becomes in the standard SOP form, but its value is not affected.

### Example 1:

The following function is written in the SOP form: F(A,B,C)=A+BC'+A'BC

#### Solution 1:

The inputs to the function F are A, B and C. In each term the inputs are ANDed then all terms are ORed to form the function F. The last term A'BC contains all the inputs of the function (A, B and C), so, this term is written in standard form. But the second term BC' is not in standard form because the input A does not exist, then multiply by (A'+A). The same is done for the remaining term as follows: F(A,B,C)=A(B+B')(C+C')+BC'(A+A')+A'BC

$$F(A,B,C)=ABC+ABC'+AB'C+AB'C'+ABC'+A'BC'+A'BC'$$

$$=ABC+ABC'+AB'C+AB'C'+A'BC'+A'BC'$$

The Product-of-Sum (POS):

POS form means that the inputs of each term are Added together using OR function then all terms are multiplied together using AND function. The variables in each term are not necessarily all the variables of the function. For example, a POS of F(A,B,C) may contain a term that contains only the variable A but not B nor C, in such case the term is not in its standard POS form. Standard POS term must contain all the function variables. From Boolean algebra thermos (X.X'=0), then if the term is added to (X.X'), it becomes in the standard POS form, but its value is not affected.

#### Example 2:

The following function is written in the POS form:

F(A,B,C)=A.(B+C').(A'+B+C')

#### Solution 2:

The inputs to the function F are A, B and C. In each term the inputs are ORed then all terms are ANDed to form the function F. The last term (A'+B+C') contains all the inputs of the function (A, B and C), so, this term is written in standard form. But the second term (B+C') is not in standard form because the input A does not exist, then add (A'.A). The same is done for the remaining term as follows:

$$\begin{split} F(A,B,C) &= [A+(B.B')+(C.C')].[(B+C')+(A.A')].(A'+B+C') \\ F(A,B,C) &= [(A+B+C).(A+B+C').(A+B'+C).(A+B'+C')].[(A+B+C').(A'+B+C')].(A'+B+C') \\ &= (A+B+C).(A+B+C').(A+B'+C).(A+B'+C').(A'+B+C') \ Minterms \end{split}$$

Writing a function in its minterm format is equivalent to writing the function in its standard SOP format such that the value of the function at these terms is 1. So that if we have the truth table relating the input variables to the function F, then we can determine which cases result in F=1 and write the minterm form of the function.

#### Maxterms

Writing a function in its maxterm format is equivalent to writing the function in its standard POS format such that the value of the function at these terms is 0. So that if we have the truth table relating the input variables to the function F, we can determine which cases result in F=0 and write the maxterm form of the function.

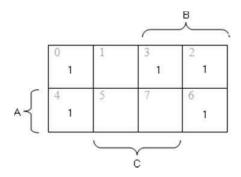

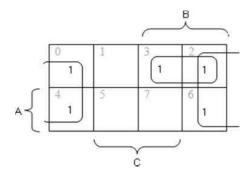

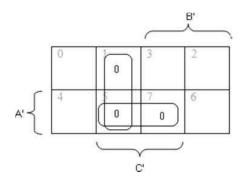

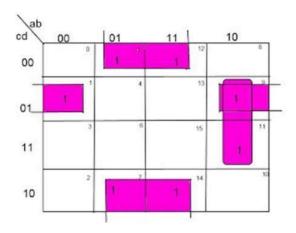

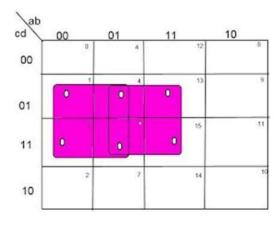

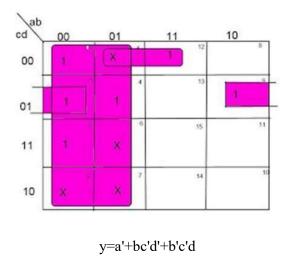

### Karnaugh Map

The Karnaugh map (K-map) provides a systematic way of simplifying Boolean algebra expressions. This can be done without thoroughly searching the basic theorems of Boolean algebra. Instead all the possible combinations of the variables written in the standard form for POS (product of sums) or SOP (sums of products) are plotted in cells arranged in a rectangle or square. Adjacent cells share a redundant Boolean variable. The simplification of the original Boolean expression comes form grouping the logical one s (minterms) or 0 s (maxterms). This eliminates the redundant variable and simplifies the original Boolean expression.

The circulation must be done according to the following rules:

- 1. A group must contain either 1, 2, 4, 8, 16 ...cells.

- 2. Each cell in a group must be adjacent to one or more cells in the same group, but all cells do not have to be adjacent to each other.

- 3. ALWAYS include the most possible of 1 s in a group in accordance to rule (1).

- 4. Each 1 on the K-map must be included in at least one group. The 1 s in a group can be included in another group as long as the overlapping groups include non common 1 s.

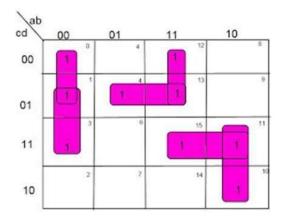

### Example 3:

Simply the following function using K-map

F(A,B,C)=A'B+ABC'+B'C'

#### Solution 3:

In order to use the K-map the function should be written in its min or max terms format.

F(A,B,C)=A'BC+A'BC'+ABC'+AB'C'+A'B'C'

$F(A,B,C)=\Sigma(0,2,3,4,6)$

To write the function as simplified SOP then circle the 1's in K-map

From K-map

F(A,B,C)=C'+BA'

F is written in max term as follows

$F(A,B,C) = \Pi(1,5,7)$

To write the function as POS then circle the 0's in K-map

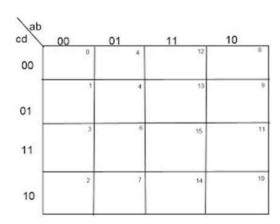

From K-map F(A,B,C)=(A'+C').(B+C')Syntax of 4 Variable K-Map:-

# ex 1- $Z=\Sigma(0,1,3,5,10,11,12,13,15)...SOP$

y=a'b'c'+a'b'd+bc'd+abc'+acd+ab'c

# ex 2- $Z=\Sigma(0,2,5,8,7,10,13,15)$

y=bd+b'd'(XOR)

Ex 3 -  $Z=\Sigma(4,1,9,6,12,14,11)$

y=bd'+ab'd+a'b'd

# Ex 4 - $S=\Pi(1,5,7,3,7,13,15)$ ..POS

$$y=(a'+d').(b'+d')$$

Don't Care Condition(K-Map):-We use Don't care condition in K-Map because to make a group of 2 variable.

$$y=\Sigma(0,1,3,5,9,12)+\Sigma d(2,4,6,7)$$

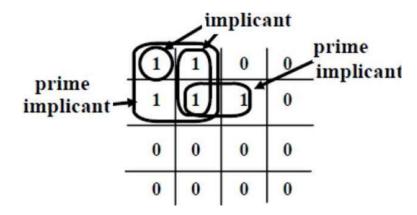

# Quine-McCluskeyAlgorithm

The method involves two steps:

- 1. Finding all prime implicants of the function.

- 2. Use those prime implicants in a prime implicantchartto find the essential prime implicants of the function, as well as other prime implicants that are necessary to cover the function.

Implicant: A single 1, or group of 1's combined together on a map, is called an implicant of F.

Prime Implicant:An implicantwhich cannot further combine with other implicantsis called a Prime Implicant of F. A prime implicate is a group of 1,2,4,8 that cannot be contained in any larger group.

### Prime implicant

- 1. Single 1 on a K-map represents a prime implicantif it is not adjacent to any other 1

- 2. Two adjacent 1 s on a K-map form a prime implicantif they are not contained in a group of four 1 s

- 3. Four adjacent 1 s on a K-map form a prime implicantif they are not contained in a group of eight 1 s

### **Essential Prime Implicant**

- 1.If minterm can be covered by only one prime implicant, then that prime implicant is called an Essential Prime Implicant

- 2.All essential prime implicants must be present in the minimum expression for F.

- 3. Therefore find all essential prime implicants first.

examine each 1 on map

if that 1 + all adjacent 1's covered by one term only (i.e. encircled by one loop only), that term is essential cover remaining 1's by minimum set of prime implicants

### Groups of the minterms

1. Forms Groups of the mintermsis the following ways.

Group 1: terms with no 1s.

Group 2: terms which have only one 1.

Group 3 terms which have only two 1s and so on..

The terms should be written in the ascending order of their values.

Example: 0001, 1000, 0100, 0010 should be written as 0001, 0010, 0100, 1000 and forms group 2.

Each group has an equal number of ones in the input combination.

2. Each mintermean only be adjacent to the minterms in the next group.

#### **Combining Minterms**

2. Any two minterms which differ from each other by only one variable can be combined, and the unmatched variable removed (by marking - or x).

E.g., 0000 vs. 0100 yields 0-00 or 0x00 0000 vs. 1000 yields -000 or x000

- 3. When used in a combination, mark with a check. If cannot be combined, mark with a star. These are the prime implicants.

- 4. Continue again. Pair up rows from adjacent regions if they differ by exactly one bit.

- 5. Repeat until nothing left.

#### Prime implicantchart

1The table is required to find essential prime implicant

2 Prime-implicanttable rows = prime implicants columns = minterms of the function place an "X" if the mintermis covered by the prime implicant.

If column has a single X, than the implicant associated with the row is essential. It must appear in minimum cover as well as other prime implicant sthat are necessary to cover the function.

Example: Determine the prime implicants of the function given below

|      | F(w,x, | $(y,z)=\sum (1,4)$ | 4,6,7,8,9,10,11,15) | )   |            |                     |

|------|--------|--------------------|---------------------|-----|------------|---------------------|

|      | (a)    |                    |                     | (b) |            | (c)                 |

| 0001 | 1      | <b>√</b>           | 1, 9                | (8) |            | 8, 9, 10, 11 (1, 2) |

| 0100 | 4      | ✓                  | 4, 6                | (2) |            | 8, 9, 10, 11 (1, 2) |

| 1000 | 8      | /                  | 8, 9                | (1) | <b>-</b> √ |                     |

| · ·  |        |                    | 8, 10               | (2) | <b>√</b>   |                     |

| 0110 | 6      | $\checkmark$       |                     |     |            |                     |

| 1001 | 9      | ✓                  | 6, 7                | (1) |            |                     |

| 1010 | 10     | ✓                  | 9, 11               | (2) | ✓          |                     |

|      |        |                    | 10, 11              | (1) | <b>/</b>   |                     |

| 0111 | 7      | /                  |                     |     |            |                     |

| 1011 | 11     | ✓                  | 7, 15               | (8) |            |                     |

|      |        |                    | 11, 15              | (4) |            |                     |

| 1111 | 15     | $\checkmark$       | -                   |     |            |                     |

Prime implicants

| Decimal             | W | X | y | Z | Term  |

|---------------------|---|---|---|---|-------|

| 1, 9 (8)            | _ | 0 | 0 | 1 | x'y'z |

| 4, 6 (2)            | 0 | 1 | _ | 0 | w'xz' |

| 6, 7 (1)            | 0 | 1 | 1 | _ | w'xy  |

| 7, 15 (8)           | _ | 1 | 1 | 1 | xyz   |

| 11, 15 (4)          | 1 | _ | 1 | 1 | wyz   |

| 8, 9, 10, 11 (1, 2) | 1 | 0 | _ |   | wx'   |

# Prime implicant chart

- Eliminate all columns covered by essential primes

- •Find minimum set of rows that cover the remaining columns

|                |              | 1 | 4                | 6                | 7                | 8 | 9                | 10                                     | 11 | 15 |

|----------------|--------------|---|------------------|------------------|------------------|---|------------------|----------------------------------------|----|----|

| $\sqrt{x'y'z}$ | 1, 9         | X |                  |                  |                  |   | X                | »————————————————————————————————————— |    |    |

| √w'xz'         | 4, 6         |   | $\boldsymbol{X}$ | $\boldsymbol{X}$ |                  |   |                  |                                        |    |    |

| w'xy           | 6, 7         |   |                  | X                | $\boldsymbol{X}$ |   |                  |                                        |    |    |

| xyz            | 7, 15        |   |                  |                  | X                |   |                  |                                        |    | X  |

| wyz            | 11, 15       |   |                  |                  |                  |   |                  |                                        | X  | X  |

| √ wx'          | 8, 9, 10, 11 |   |                  |                  |                  | X | $\boldsymbol{X}$ | X                                      | X  |    |

|                |              | ✓ | <b>/</b>         | <b>\</b>         |                  | / | <b>√</b>         | <b>/</b>                               |    | _  |

Prime implicant chart

|                |              | 1       | 4                | 6                | 1                | 8 | 9                | 10       | 11 | 15               |

|----------------|--------------|---------|------------------|------------------|------------------|---|------------------|----------|----|------------------|

| $\sqrt{x'y'z}$ | 1, 9         | X       |                  |                  |                  |   | X                |          |    | 1.75             |

| √w'xz'         | 4, 6         |         | $\boldsymbol{X}$ | $\boldsymbol{X}$ |                  |   |                  |          |    |                  |

| w'xy           | 6, 7         |         |                  | X                | $\boldsymbol{X}$ |   |                  |          |    |                  |

| xyz            | 7, 15        |         |                  |                  | X                |   |                  |          |    | X                |

| wyz            | 11, 15       |         |                  |                  |                  |   |                  |          | X  | $\boldsymbol{X}$ |

| √ wx′          | 8, 9, 10, 11 |         |                  |                  |                  | X | $\boldsymbol{X}$ | X        | X  |                  |

|                |              | <u></u> | /                | /                |                  | / | <b>/</b>         | <b>/</b> |    |                  |

the table shows that the selection of essential prime implicantscovers all the minterms of the function except 7 and 15.

these two mintermsmust be included by the selection of one or more prime implicants.

Here xyz covers both minterms and hence one to be selected.

We have thus found the following minimum set of prime implicantswhose sum gives the required minimized function.

$$F = x'y'z + w'xz' + wx' + xyz$$

# **MODULE II**

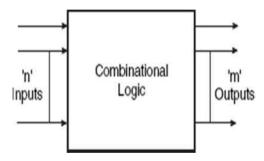

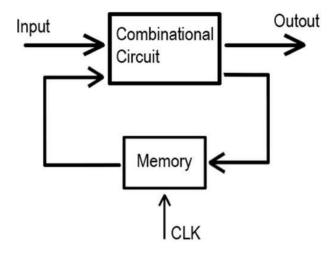

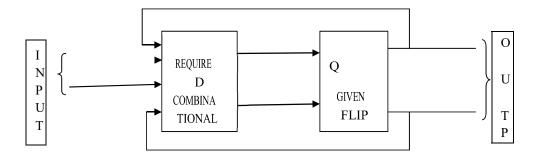

# **Combinational Circuits:**

Combinational circuit is a circuit in which we combine the different gates in the circuit, The term combinational comes to us from mathematics. In mathematics a combination is an unordered set, which is a formal way to say that nobody cares which order the items came in. Most games work this way, if you rolled dice one at a time and get a 2 followed by a 3 it is the same as if you had rolled a 3 followed by a 2. With combinational logic, the circuit produces the same output regardless of the order the inputs are changed. There are circuits which depend on the when the inputs change, these circuits are called sequential logic. Even though you will not find the term sequential logic in the chapter titles, the next several chapters will discuss sequential logic. Practical circuits will have a mix of combinational and sequential logic, with sequential logic making sure everything happens in order and combinational logic performing functions like arithmetic, logic, or conversion.

#### Design Using Gates:

A combinational circuit is one where the output at any time depends only on the present combination of inputs at that point of time with total disregard to the past state of the inputs. The logic gate is the most basic building block of combinational logic. The logical function performed by a combinational circuit is fully defined by a set of Boolean expressions. The other category of logic circuits, called sequential logic circuits, comprises both logic gates and memory elements such as flip-flops. Owing to the presence of memory elements, the output in a sequential circuit depends upon not only the present but also the past state of inputs.

Generalized Combinational Circuit

This Figure shows the block schematic representation of a generalized combinational circuit having n input variables and m output variables or simply outputs. Since the number of input variables is n, there are 2n possible combinations of bits at the input. Each output can be expressed in terms of input.

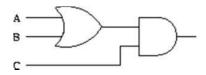

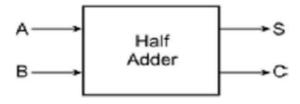

#### Half-Adder Circuit

A half-adder is an arithmetic circuit block that can be used to add two bits. Such a circuit thus has two inputs that represent the two bits to be added and two outputs, with one producing the SUM output and the other producing the CARRY. Figure shows the truth table of a half- adder, showing all possible input combinations and the corresponding outputs.

Block Diagram of Half Adder Circuit

| Α | В | s | С |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

Truth Table of Half Adder

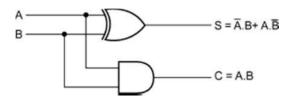

The Boolean expressions for the SUM and CARRY outputs are given by the equations below-

SUM

$$S = A.B ++ A.B$$

$CARRY C = A.B$

An examination of the two expressions tells that there is no scope for further simplification. While the first one representing the SUM output is that of an EX-OR gate, the second one representing the CARRY output is that of an AND gate. However, these two expressions can certainly be represented in different forms using various laws

and theorems of Boolean algebra to illustrate the flexibility that the designer has in hardware- implementing as simple a combinational function as that of a half-adder.

#### Logic Implementation of Half Adder

Although the simplest way to hardware-implement a half-adder would be to use a two-input EX-OR gate for the SUM output and a two-input AND gate for the CARRY output, as shown in Figure, it could also be implemented by using an appropriate arrangement of either NAND or NOR gates.

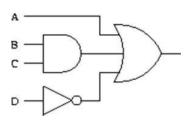

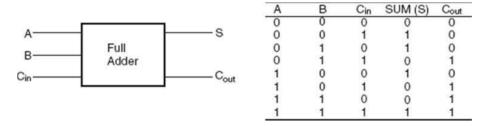

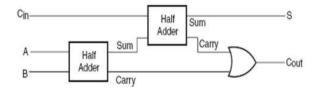

#### Full Adder Circuit

A full adder circuit is an arithmetic circuit block that can be used to add three bits to produce a SUM and a CARRY output. Such a building block becomes a necessity when it comes to adding binary numbers with a large number of bits. The full adder circuit overcomes the limitation of the half-adder, which can be used to add two bits only. Let us recall the procedure for adding larger binary numbers. We begin with the addition of LSBs of the two numbers. We record the sum under the LSB column and take the carry, if any, forward to the next higher column bits. As a result, when we add the next adjacent higher column bits, we would be required to add three bits if there were a carry from the previous addition. We have a similar situation for the other higher column bits. Also until we reach the MSB. A full adder is therefore essential for the hardware implementation of an adder circuit capable of adding larger binary numbers. A half-adder can be used for addition of LSBs only. Figure shows the truth table of a full adder circuit showing all possible input combinations and corresponding outputs. In order to arrive at the logic circuit for hardware implementation of a full adder, we will firstly write the Boolean expressions for the two output variables, that is, the SUM and

CARRY outputs, in terms of input variables. These expressions are then simplified

Block Diagram of Full Adder Circuit and Truth Table of Full Adder:

by using any of the simplification techniques described in the previous chapter. The Boolean expressions for the two output variables are given in Equation below for the SUM output (S) and in above Equation for the CARRY output (Cout):

$$\begin{split} S &= \overline{A}.\overline{B}.C_{\text{in}} + \overline{A}.B.\overline{C}_{\text{in}} + A.\overline{B}.\overline{C}_{\text{in}} + A.B.C_{\text{in}} \\ C_{\text{out}} &= \overline{A}.B.C_{\text{in}} + A.\overline{B}.C_{\text{in}} + A.B.\overline{C}_{\text{in}} + A.B.C_{\text{in}} \end{split}$$

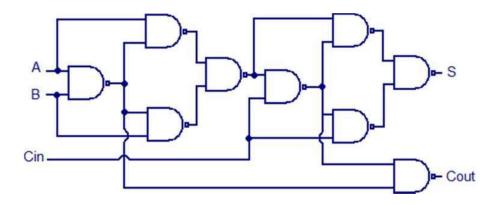

The next step is to simplify the two expressions. Logic circuit diagram of full adder Boolean expression above can be implemented with a two-input EX-OR gate provided that one of the inputs is Cin and the other input is the output of another two-input EX-OR gate with A and B as its inputs. Similarly, Boolean expression above can be implemented by ORing two minterms. One of them is the AND output of A and B. The other is also the output of an AND gate whose inputs are Cin and the output of an EX-OR operation on A and B. The whole idea of writing the Boolean expressions in this modified form was to demonstrate the use of a half-adder circuit in building a full adder. In the above it shows logic implementation of Equations. However, a single full adder circuit can be used to add one-bit binary numbers only. A cascade arrangement of these adders can be used to construct adders capable of adding binary numbers with a larger number of bits. For example, a four-bit binary adder would require four full adders of the type shown in Figure to be connected in cascade. After minimization we get the following logic circuit-

Logic circuit of Full Adder

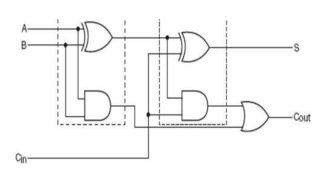

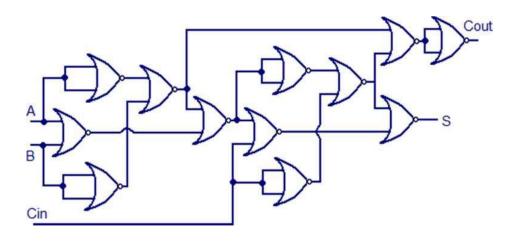

### Full adder using NAND or NOR logic

Alternatively the full adder can be made using NAND or NOR logic. These schemes are universally accepted and their circuit diagrams are shown below.

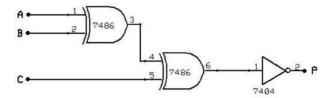

Full adder using NAND Gates

Full adder using NOR Gates

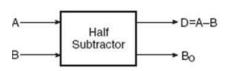

#### Half-Subtractor Circuit

We will study the use of adder circuits for subtraction operations in the following pages. Before we do that, we will briefly look at the counterparts of half-adder and full adder circuits in the half-subtractor and full subtractor for direct implementation of subtraction operations using logic gates. A half-subtractor is a combinational circuit that can be used to subtract one binary digit from another to produce a

| Α | В | D | Bo |

|---|---|---|----|

| 0 | 0 | 0 | 0  |

| 0 | 1 | 1 | 1  |

| 1 | 0 | 1 | 0  |

| 1 | 1 | 0 | 0  |

output and a BORROW output.

Block Diagram of Half Subtractor Circuit and Truth Table of Half Subtractor:

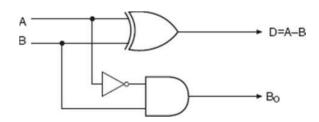

The BORROW output here specifies whether a '1' has been borrowed to perform the subtraction. The truth table of a half-subtractor, as shown in Figure, explains this further. The Boolean expressions for the two outputs are given by the equations

$$D = \overline{A}.B + A.\overline{B}$$

$$B_0 = \overline{A}.B$$

It is obvious that there is no further scope for any simplification of the Boolean expressions given by above equations. While the expression for the DIFFERENCE (D) output is that of an EX-OR gate, the expression for the BORROW output (Bo) is that of an AND gate with input A complemented before it is fed to the gate. Figure shows the logic implementation of a half-subtractor. Comparing a half-subtractor with a half-adder, we find that the expressions for the SUM and DIFFERENCE outputs are just the same. The expression for BORROW in the case of the half-subtractor is also similar to what we have for CARRY in the case of the half-adder. If the input A, that is, the minuend, is complemented, an AND gate can be used to implement the BORROW output.

Logic Diagram of a Half Subtractor

It is obvious that there is no further scope for any simplification of the Boolean expressions given by above equations. While the expression for the DIFFERENCE (D) output is that of an EXOR gate, the expression for the BORROW output (Bo) is that of an AND gate with input A complemented before it is fed to the gate. This Figure shows the logic implementation of a halfsubtractor. Comparing a half- subtractor with a half-adder, we find that the expressions for the SUM and DIFFERENCE outputs are just the same. The expression for BORROW in the case of the halfsubtractor is also similar to what we have for CARRY in the case of the half-adder. If the input A, that is, the minuend, is complemented, an AND gate can be used to implement the BORROW output.

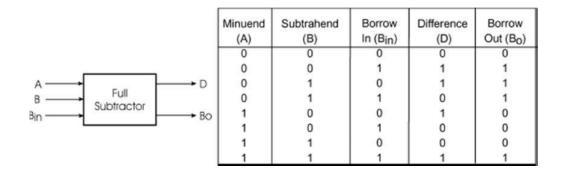

#### Full Subtractor Circuit

A full subtractor performs subtraction operation on two bits, a minuend and a subtrahend, and also takes into consideration whether a '1' has already been borrowed by the previous adjacent lower minuend bit or not. As a result, there are three bits to be handled at the input of a full subtractor, namely the two bits to be subtracted and a borrow bit designated as Bin . There are two outputs, namely the DIFFERENCE output D and the BORROW output Bo.

Block Diagram of Full Subtractor Circuit and Truth Table of Full Subtractor:

The BORROW output bit tells whether the minuend bit needs to borrow a '1' from the next possible higher minuend bit. Figure shows the truth table of a full subtractor. The Boolean expressions for the two output variables are given by the equations-

$$D = \overline{A}.\overline{B}.B_{in} + \overline{A}.B.\overline{B}_{in} + A.\overline{B}.\overline{B}_{in} + A.B.B_{in}$$

$$B_{o} = \overline{A}.\overline{B}.B_{in} + \overline{A}.B.\overline{B}_{in} + \overline{A}.B.B_{in} + A.B.B_{in}$$

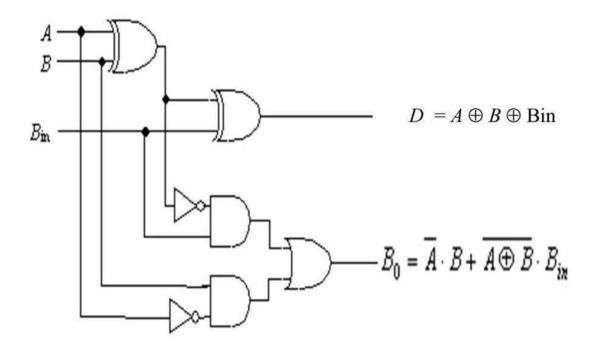

After minimizing the above expressions we get-

$$D = A \oplus B \oplus Bin$$

$$B_0 = \overline{A} \cdot B + \overline{A \oplus B} \cdot B_{in}$$

Logic circuit of Full Subtractor

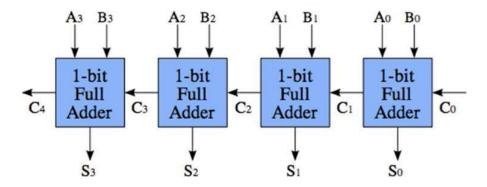

#### N-Bit Parallel Adder

The Full Adder is capable of adding only two single digit binary number along with a carry input. But in practical we need to add binary numbers which are much longer than just one bit. To add two nbit binary numbers we need to use the n-bit parallel adder. It uses a number of full adders in cascade. The carry output of the previous full adder is connected to carry input of the next full adder.

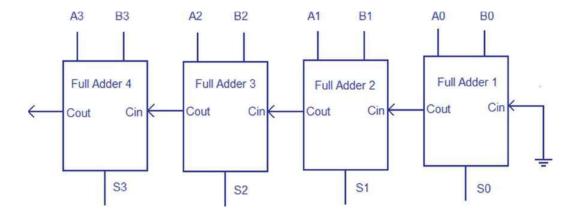

# 4 Bit Parallel Adder

In the block diagram, A 0 and B 0 represent the LSB of the four bit words A and B. Hence Full Adder- 0 is the lowest stage. Hence its Cin has been permanently made 0. The rest of the connections are exactly same as those of n-bit parallel adder is shown in fig. The four bit parallel adder is a very common logic circuit.

Block diagram of 4 Bit Parallel Adder

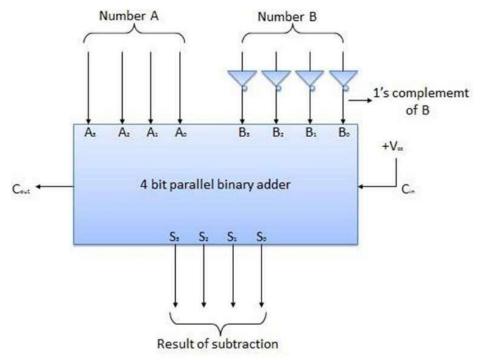

#### N-Bit Parallel Subtractor

The subtraction can be carried out by taking the 1's or 2's complement of the number to be subtracted. For example we can perform the subtraction A - B by adding either 1's or 2's complement of B to A. That means we can use a binary adder to perform the binary subtraction.

#### 4 Bit Parallel Subtractor

The number to be subtracted B is first passed through inverters to obtain its 1's complement. The 4-bit adder then adds A and 2's complement of B to produce the subtraction. S3 S2 S1 S0 represents the result of binary subtraction A-B and carry output Cout represents the polarity of the result. If A>B then Cout = 0 and the result of binary form A-B then Cout = 1 and the result is in the 2's complement form.

Block diagram of 4 Bit Parallel Subtractor

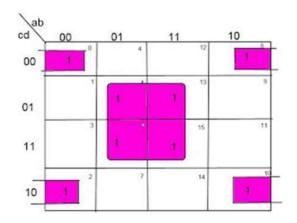

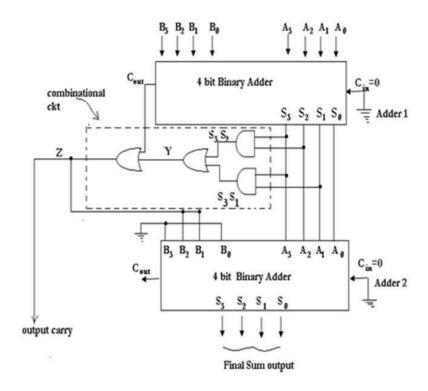

BCD Adder:

BCD binary numbers represent Decimal digits 0 to 9. A 4-bit BCD code is used to represent the ten numbers 0 to 9. Since the 4-bit Code allows 16 possibilities, therefore the first 10 4-bit combinations are considered to be valid BCD combinations. The latter six combinations are invalid and do not occur.BCD Code has applications in Decimal Number display Systems such as Counters and Digital Clocks. BCD Numbers can be added together using BCD Addition. BCD Addition is similar to normal Binary Addition except for the case when sum of two BCD digits exceeds 9 or a Carry is generated. When the Sum of two BCD numbers exceeds 9 or a Carry is generated a 6 is added to convert the invalid number into a valid number. The carry generated by adding a 6 to the invalid BDC digit is passed on to the next BCD digit. Addition of two BCD digits requires two 4-bit Parallel Adder Circuits. One 4-bit Parallel Adder adds the two BCD digits. A BCD Adder uses a circuit which checks the result at the output of the first adder circuit to determine if the result has exceeded 9 or a Carry has been generated. A BCD adder adds two BCD digits and produces output as a BCD digit. A BCD or Binary Coded Decimal digit cannot be greater than 9.

- The two BCD digits are to be added using the rules of binary addition. If sum is less than or equal to 9 and carry is 0, then no correction is needed. The sum is correct and in true BCD form.

- But if sum is greater than 9 or carry =1, the result is wrong and correction must be done. The wrong result can be corrected adding six (0110) to it.

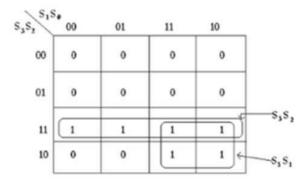

- For implementing a BCD adder using a binary adder circuit IC 7483, additional combinational circuit will be required, where the Sum output \$S\_3-S\_0\$ is checked for invalid values from 10 to 15. The truth table and K-map for the same is as shown:

|    | I/ | P  |    | O/P |

|----|----|----|----|-----|

| S3 | S2 | S1 | S0 | Y   |

| 0  | 0  | 0  | 0  | 0   |

| 0  | 0  | 0  | 1  | 0   |

| 0  | 0  | 1  | 0  | 0   |

| 0  | 0  | 1  | 1  | 0   |

| 0  | 1  | 0  | 0  | 0   |

| 0  | 1  | 0  | 1  | 0   |

| 0  | 1  | 1  | 0  | 0   |

| 0  | 1  | 1  | 1  | 0   |

| 1  | 0  | 0  | 0  | 0   |

| 1  | 0  | 0  | 1  | 0   |

| 1  | 0  | 1  | 0  | 1   |

| 1  | 0  | 1  | 1  | 1   |

| 1  | 1  | 0  | 0  | 1   |

| 1  | 1  | 0  | 1  | 1   |

| 1  | 1  | 1  | 0  | 1   |

| 1  | 1  | 1  | 1  | 1   |

K- Map for the above Truth table

Logic circuit of BCD Adder

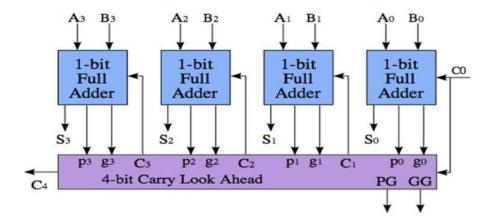

#### Carry-look ahead Adder:

A system of ripple-carry adders is a sequence of standard full adders that makes it possible to add numbers that contain more bits than that of a single full adder. Each full adder has a carry in (Cin) and a carryout (Cout) bit, and the adders are connected by connecting Cout on step k to Cin on step k+1 (Cin on step 0 is C0 in the Figure, Cout on step 3 is C4 in the Figure)

The challenge with ripple-carry adders, is the propagation delay of the carry bits. Assume that, in an instant the values of A and B change, such that

$$A1 = 0$$

$B1 = 1 A0$

$= 1$

$B0 = 1$

Since A0 and B0 are high, the first full adder will produce a carry, i. e. C1 = 1. However, it takes some time for the logic to settle down, so C1 doesn't change until a little after A1 and B1 changed. Thus, before C1 shows up, the second full adder does not produce a carry, but as C1 shows up, the second adder will recompute and produce a carry, i. e. C2 = 1. In the worst case, C4 is not correctly computed until 4\*propagation delay, and Cn is not computed until n\*propagation delay.

A carry-lookahead adder system solves this problem, by computing whether a carry will be generated before it actually computes the sum. There are multiple schemes of doing this, so there is no "one" circuit that constitutes a look-ahead adder. The idea is something like this:

Logic circuit of 4 bit Carry-lookahead Adder

The calculation of C4 is no faster than in the the ripple-carry above, nor is PG and GG - the magic only happens when you put several of these blocks together to add even larger numbers.

The important to note part of the picture, is that the purple block is producing three values: C4, PG (Propagate) and GG (Generate). PG goes high if this block will propagate Cin to Cout, and GG goes high if the block will generate an overflow regardless of Cin. (Also, the block may neither propegate nor generate a carry, in which case both PG and GG are low, and Cout is 0.) PG and GG can be calculated in the purple block regardless of the value of C0 - thus, when C0 finally arrives, the purple block can simply consult its previously calculated result, and if the result is a "propagate," then C0 is propagated directly to C4; this is four times faster than propagating through all the four full adders.

### Assignment:

- 1. Draw the Half Subtractor circuit using two input NOR gate.

- 2. Draw the Half Subtractor circuit using two input NOR gate.

- 3. Draw a logic circuit that has three inputs A, B and C and whose output will be high only when majority inputs are high.

- 4. (A) What is the number of carry-lookahead levels L in a 128-bit carry-lookahead adder using the same component types are in Figure 2? (B) How many carry-lookahead circuits are required?

- (c) What is the estimated maximum delay through the 128-bit adder assuming that each gate delay is 0.20 ns?

#### Model Questions:

- 1. A binary parallel adder produces arithmetic sum in

- a. serial

- b. parallel

- c. sequence

- d. both a and b

- 2. Sum of two n-bit binary numbers can be done

- a. serially

- b. parallely

- c. sequentially

- d. both a and b

- 3. Full adder forms sum of

- a. 2bits

- b. 3bits

- c. 4bits

- d. 5bits

- 4. Subtraction of binary numbers can be done conveniently with

- a. high cost circuit

- b. low cost circuits

- c. complements

- d. borrows

- 5. The sum of a Full adder can be represented by

- a. 2 input X-OR gate

- b. 3 input NAND gate

- c. 2 input NAND gate

- d. 3 input X-OR gate

- 6. Draw the circuit diagram of Half Adder using NAND gate only. Describe the operation performed by Half adder.

- 7. Draw a block diagram of a full adder labeling all the inputs and outputs. Write the truth table for full adder.

- 8. Draw the circuit diagram of Half Subtractor using NAND gate only. Describe its operation.

- 9. Draw a block diagram of a full Subtractor labeling all the inputs and outputs. Write the truth table for full Subtractor.

- 19. Draw the Half Adder circuit using two input NOR gate.

- 11. Draw the Full Adder circuit using two input NOR gate.

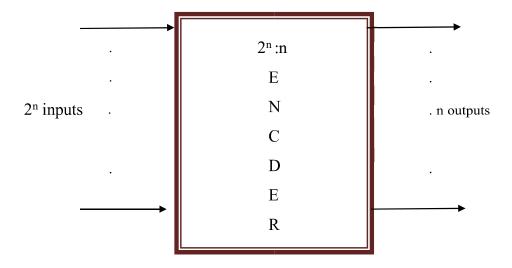

# Encoder:

It is a circuit which accepts an active level(high level or low level) from one of its  $2^n$  or less (in some cases) inputs which representing a digit and converts it to a n bit coded output. For an example 2 to 1,4 to 2,8 to 3 also called octal to binary,10 to 4 also called decimal to BCD,16 to 4 encoder etc.It can encode symbols or characters also.

Block diagram of encoder

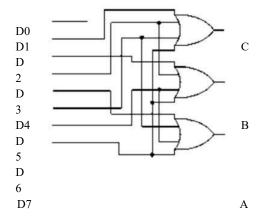

8 to 3(Octal to Binary) Encoder Design:

It accepts 8 inputs & produces 3 bit coded output according to the activated input. Here active high logic is used for activated input.

Truth Table

| Input | Input |    |    |    |    |    |    |   |   | Output |  |  |

|-------|-------|----|----|----|----|----|----|---|---|--------|--|--|

| D0    | D1    | D2 | D3 | D4 | D5 | D6 | D7 | A | В | С      |  |  |

| 1     | 0     | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0      |  |  |

| 0     | 1     | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 1      |  |  |

| 0     | 0     | 1  | 0  | 0  | 0  | 0  | 0  | 0 | 1 | 0      |  |  |

| 0     | 0     | 0  | 1  | 0  | 0  | 0  | 0  | 0 | 1 | 1      |  |  |

| 0     | 0     | 0  | 0  | 1  | 0  | 0  | 0  | 1 | 0 | 0      |  |  |

| 0     | 0     | 0  | 0  | 0  | 1  | 0  | 0  | 1 | 0 | 1      |  |  |

| 0     | 0     | 0  | 0  | 0  | 0  | 1  | 0  | 1 | 1 | 0      |  |  |

| 0     | 0     | 0  | 0  | 0  | 0  | 0  | 1  | 1 | 1 | 1      |  |  |

Output Expression

A=D4+D5+D6+D7

B=D2+D3+D6+D7

C=D1+D3+D5+D7

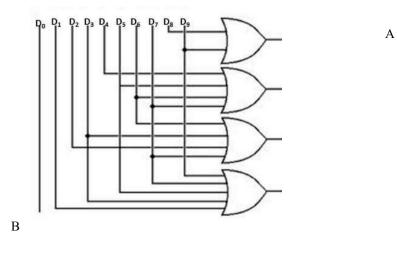

### Circuit Diagram

Circuit of 8 to 3(octal to binary) encoder

# Decimal to BCD(10 to 4) Encoder:

It accepts 10 inputs & produces 4 bit coded output according to the activated input. Here active high logic is used for activated input.

Truth Table

|       | Input          |       |       |                |                |       |       |       |                |   | Output |   |   |

|-------|----------------|-------|-------|----------------|----------------|-------|-------|-------|----------------|---|--------|---|---|

| $D_0$ | $\mathbf{D}_1$ | $D_2$ | $D_3$ | D <sub>4</sub> | $\mathbf{D}_5$ | $D_6$ | $D_7$ | $D_8$ | D <sub>9</sub> | A | В      | С | D |

| 1     | 0              | 0     | 0     | 0              | 0              | 0     | 0     | 0     | 0              | 0 | 0      | 0 | 0 |

| 0     | 1              | 0     | 0     | 0              | 0              | 0     | 0     | 0     | 0              | 0 | 0      | 0 | 1 |

| 0     | 0              | 1     | 0     | 0              | 0              | 0     | 0     | 0     | 0              | 0 | 0      | 1 | 0 |

| 0     | 0              | 0     | 1     | 0              | 0              | 0     | 0     | 0     | 0              | 0 | 0      | 1 | 1 |

| 0     | 0              | 0     | 0     | 1              | 0              | 0     | 0     | 0     | 0              | 0 | 1      | 0 | 0 |

| 0     | 0              | 0     | 0     | 0              | 1              | 0     | 0     | 0     | 0              | 0 | 1      | 0 | 1 |

| 0     | 0              | 0     | 0     | 0              | 0              | 1     | 0     | 0     | 0              | 0 | 1      | 1 | 0 |

| 0     | 0              | 0     | 0     | 0              | 0              | 0     | 1     | 0     | 0              | 0 | 1      | 1 | 1 |

| 0     | 0              | 0     | 0     | 0              | 0              | 0     | 0     | 1     | 0              | 1 | 0      | 0 | 0 |

| 0     | 0              | 0     | 0     | 0              | 0              | 0     | 0     | 0     | 1              | 1 | 0      | 0 | 1 |

### Output

#### **Expression**

$A=D_8+D_9$

$B=D_4+D_5+D_6+D_7$

$C=D_2+D_3+D_6+D_7$

$D = D_1 + D_3 + D_5 + D_7 + D_9$

#### Circuit Diagram

C

D

### Circuit of decimal to BCD(10 to 4) encoder

#### Application

- · Analog to digital converter

- Used in transmitter of communication system

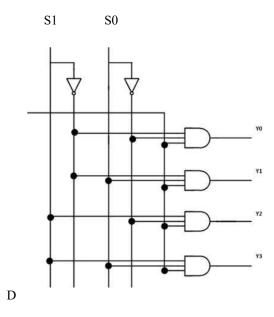

# Decoder:

It is a logic circuit that converts n bit binary input data(code) into a maximum of 2<sup>n</sup> output lines. Here each output line will be activated only for one possible combinations of inputs. For an example 1 to 2(1:2),2 to 4(2:4),3 to 8(3:8) also called binary to octal,4 to 10(4:10) also called BCD to decimal,4 to 16 (4:16) decoder etc.

#### 3 to 8 decoder design:

In this circuit only one of eight output lines is high for a particular input combination. As the inputs represent 3 bit binary numbers and the outputs represent eight digits in the octal no.

system, so it is also called binary to octal decoder.

# Truth Table

| Input |   |   | Outp  | Output         |       |       |       |                |       |       |  |  |

|-------|---|---|-------|----------------|-------|-------|-------|----------------|-------|-------|--|--|

| A     | В | С | $D_0$ | $\mathbf{D}_1$ | $D_2$ | $D_3$ | $D_4$ | D <sub>5</sub> | $D_6$ | $D_7$ |  |  |

| 0     | 0 | 0 | 1     | 0              | 0     | 0     | 0     | 0              | 0     | 0     |  |  |

| 0     | 0 | 1 | 0     | 1              | 0     | 0     | 0     | 0              | 0     | 0     |  |  |

| 0     | 1 | 0 | 0     | 0              | 1     | 0     | 0     | 0              | 0     | 0     |  |  |

| 0     | 1 | 1 | 0     | 0              | 0     | 1     | 0     | 0              | 0     | 0     |  |  |

| 1     | 0 | 0 | 0     | 0              | 0     | 0     | 1     | 0              | 0     | 0     |  |  |

| 1     | 0 | 1 | 0     | 0              | 0     | 0     | 0     | 1              | 0     | 0     |  |  |

| 1     | 1 | 0 | 0     | 0              | 0     | 0     | 0     | 0              | 1     | 0     |  |  |

| 1     | 1 | 1 | 0     | 0              | 0     | 0     | 0     | 0              | 0     | 1     |  |  |

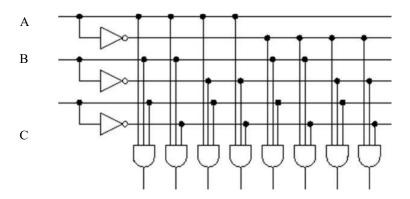

# Circuit Diagram

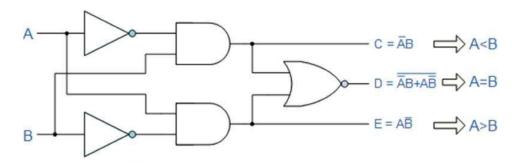

Boolean Function Representation using

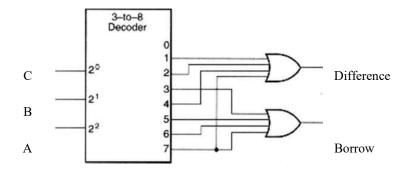

Decoder: Full Subtractor using decoder:

Truth table of full subtractor

|   | Input |   | Output     |        |  |  |

|---|-------|---|------------|--------|--|--|

| Α | В     | С | Difference | Borrow |  |  |

| 0 | 0     | 0 | 0          | 0      |  |  |

| 0 | 0     | 1 | 1          | 1      |  |  |

| 0 | 1     | 0 | 1          | 1      |  |  |

| 0 | 1     | 1 | 0          | 1      |  |  |

| 1 | 0     | 0 | 1          | 0      |  |  |

| 1 | 0     | 1 | 0          | 0      |  |  |

| 1 | 1     | 0 | 0          | 0      |  |  |

| 1 | 1     | 1 | 1          | 1      |  |  |

### Expression

Difference= $\sum m(1,2,4,7)$ Borrow= $\sum m(1,2,3,7)$

### Circuit Design

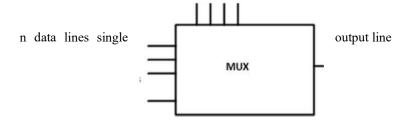

# Multiplexer(MUX):

It is a combinational circuit that selects binary information from one of many input lines and directs it to a single output line. Selection of a particular input line(called data input) is controlled by a set of control lines(called select input). A multiplexer is denoted as  $2^n$ :1 MUX where n is no. of select input and  $2^n$  is no. of data input. For an example 2 to 1(2:1),4 to 1(4:1),8 to 1(8:1),16 to 1(16:1) MUX etc.

# Block Diagram

n select input

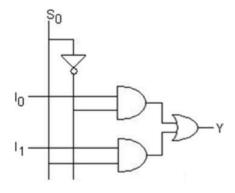

# 2:1 Multiplexers Design:

- $\bullet \hspace{0.5cm} 2 \hspace{0.1cm} \text{data input} \hspace{0.2cm} I_0, \hspace{0.1cm} I_1 \hspace{0.1cm} \square$

- 1 select lines-  $S_0 \square$

- Single output line-Y□

# Truth Table

| Data Input | Select<br>Input<br>S <sub>0</sub> | Output Y |

|------------|-----------------------------------|----------|

| $I_0$      | 0                                 | $I_0$    |

| $I_1$      | 1                                 | $I_1$    |

# Expression

$Y=S_0'I_0+S_0I_1$

# Circuit Diagram

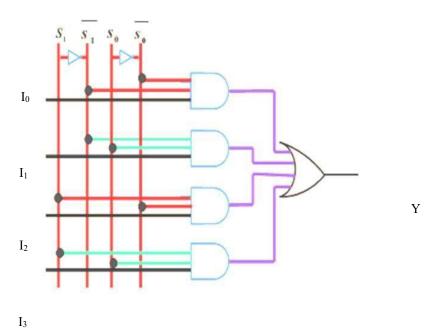

# 4:1 Multiplexers Design:

• 4 data input  $I_0$ ,  $I_1$ ,  $I_2$ ,  $I_3 \square$

- 2 select lines-  $S_1, S_0 \square$

- Single output line-

### Y Truth Table

| Data Input     | Selec | Output Y |                |

|----------------|-------|----------|----------------|

|                | $S_1$ | $S_0$    |                |

| $I_0$          | 0     | 0        | $I_0$          |

| $I_1$          | 0     | 1        | $I_1$          |

| I <sub>2</sub> | 1     | 0        | I <sub>2</sub> |

| I <sub>3</sub> | 1     | 1        | I <sub>3</sub> |

# Expression

$$Y=S_0' S_1' I_0 + S_0 S_1' I_1 + S_0' S_1 I_2 + S_0 S_1 I_3$$

### Circuit Diagram

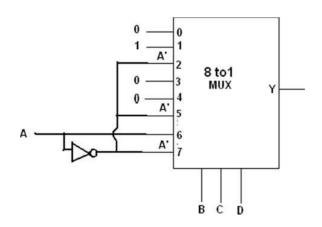

### Boolean Function Implementation Using MUX:

- One variable is chosen for input lines and rest of the term for select lines.

- The min terms with the variable selected for input are listed in two rows as implementation table □

- All the min terms which are present in the function are circled of If no circled variable in any column, then 0 is applied to the corresponding input line of If both circled variables in any column,

then 1 is applied to the corresponding input line o If bottom variable is circled and top is not circled, original variable is applied to the corresponding input line

o If bottom variable is not circled and top is circled, then complemented variable is applied to the corresponding input line

#### Examples:

Implement the function  $F(A, B, C, D) = \Sigma (1, 2, 5, 7, 9, 14)$  using MUX

Let, take the variable A for input lines and B, C & D for selection lines.

No. of variable N=4,

$2^{N-1}=2^3 => 8:1 \text{ MUX is required}$

| $I_0$ | $I_1$  | $I_2$ | $I_3$ | $I_4$ | I <sub>5</sub> | $I_6$ | $I_7$ |

|-------|--------|-------|-------|-------|----------------|-------|-------|

| 0     | $\cap$ | 0     | 2     | 1     | 0              | 6     | 0     |

| 0     |        | 2     | 3     | 4     | 3              | 0     | ~     |

| 8     | 90     | 10    | 11    | 12    | 13             | 140   | 15    |

|       |        |       |       |       |                |       |       |

| 0     | 1      | A'    | 0     | 0     | A              | A'    | A     |

Implementation Table

A'

Α

### **Designed Circuit**

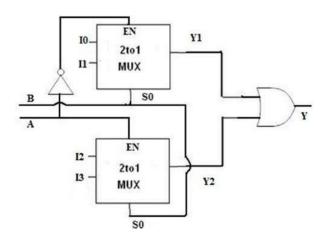

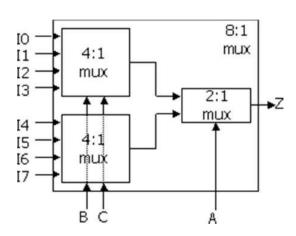

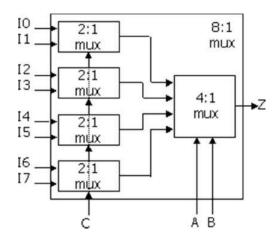

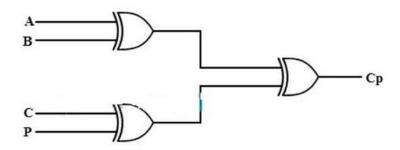

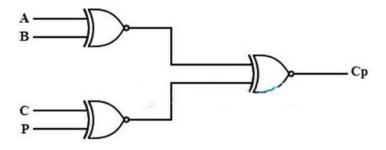

# Cascading of MUX:

# 4:1 MUX using 2:1 MUX and OR gate:

# 8:1 MUX using 4:1 MUX & 2:1 MUX:

• Using two 4:1 MUX and one 2:1

$MUX \square$

$\label{eq:Using one 4:1 MUX and four 2:1} $$ Using one 4:1 MUX and four 2:1 $$ MUX(Alternate Circuit)$

# Demultiplexer:

A demultiplexer (or demux) takes the input from single data input line and directs it to one of several digital output lines. A demultiplexer with n select lines has  $2^n$  outputs. It is also called a data distributor.

### 1 to 4 demultiplexer:

- One data input  $D\Box$

- 2 select lines (S0, S1)□

- 4 outputs (Y0 Y3)□

### Truth table

| Data Input | Select Inp | ut Y3 | Y2 | Y1 | Y0 |

|------------|------------|-------|----|----|----|

|            | S1         | S0    |    |    |    |

| D          | 0          | 0     | 0  | 0  | D  |

| D          | 0          | 1 0   | 0  | D  | 0  |

| D          | 1 0        | 0     | D  | 0  | 0  |

| D          | 1          | I D   | 0  | 0  | 0  |

### Expression

Y0=S0'S1'D

Y1 = S0S1'D

Y2 = S0'S1D

Y3 = S0S1D

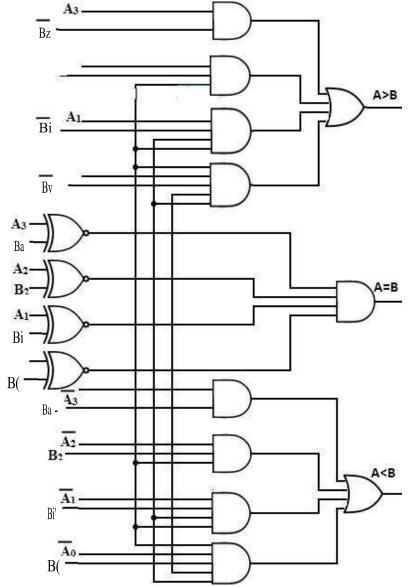

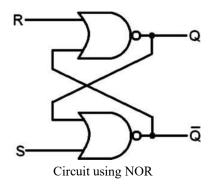

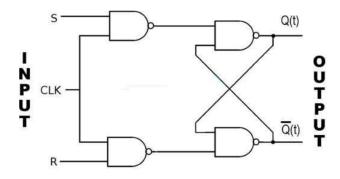

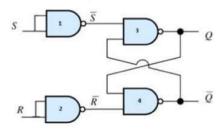

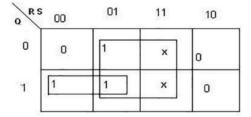

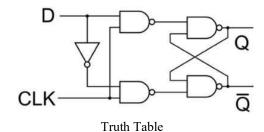

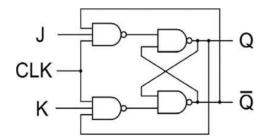

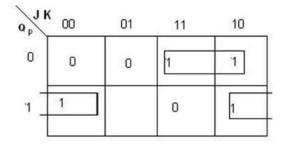

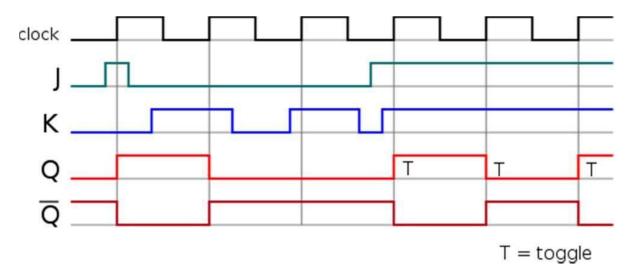

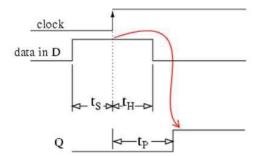

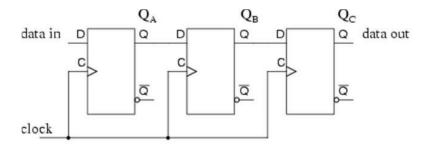

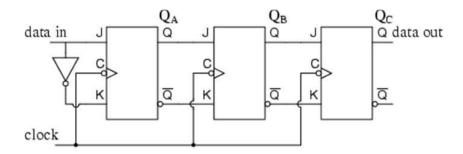

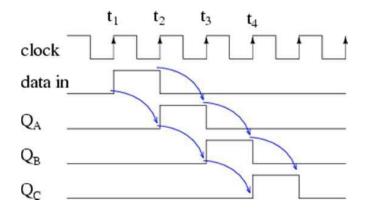

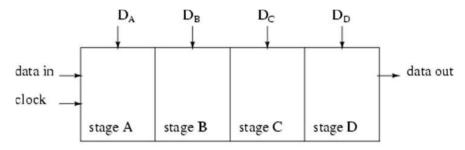

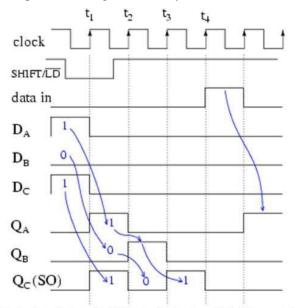

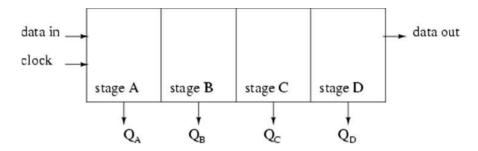

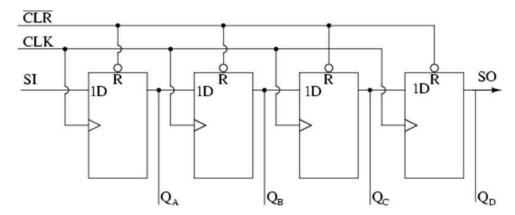

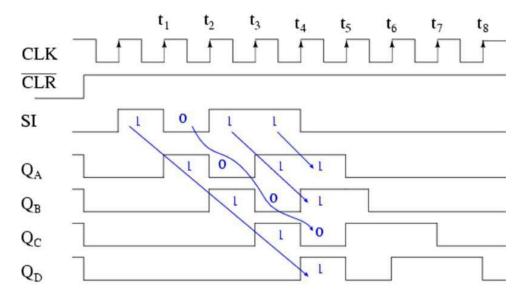

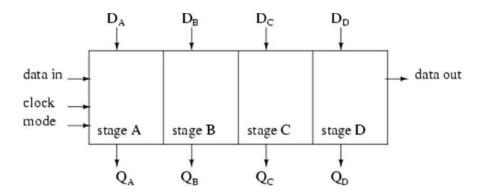

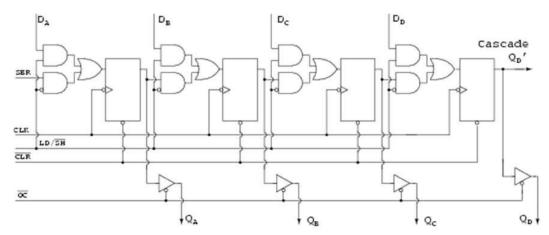

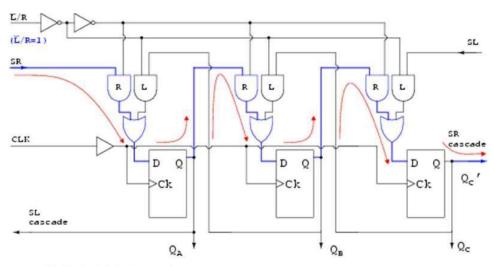

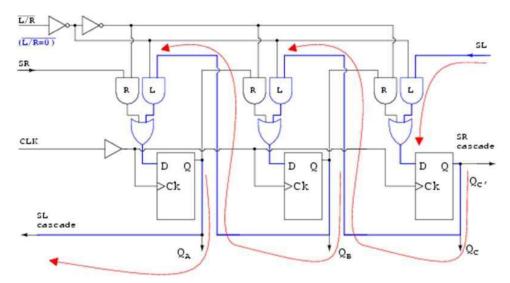

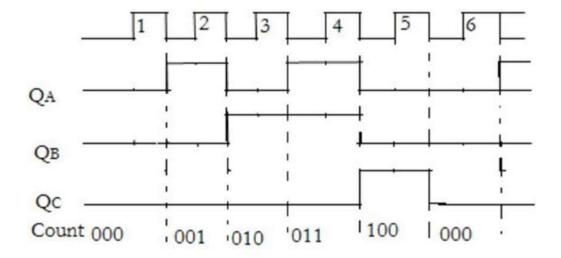

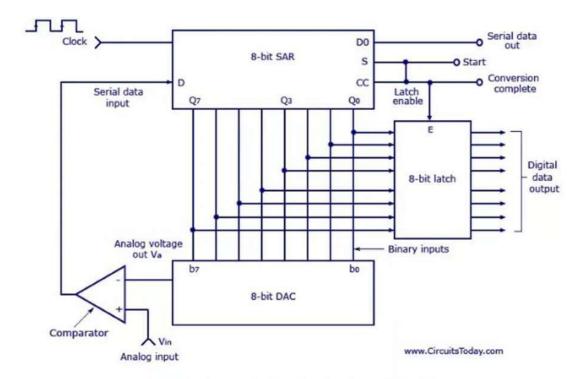

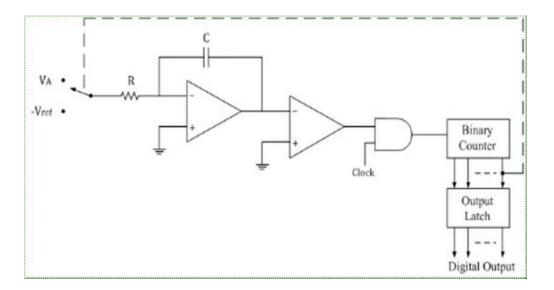

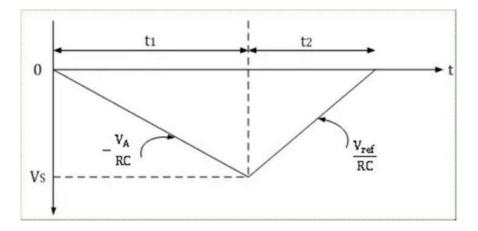

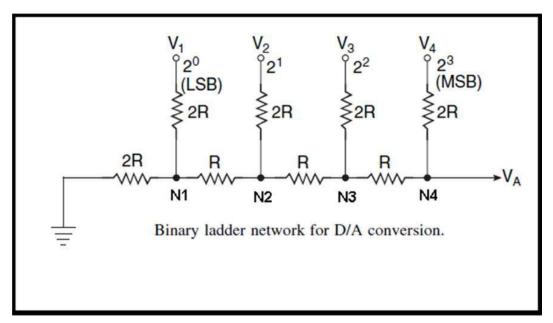

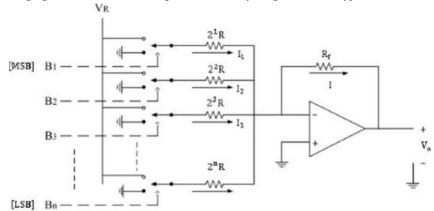

#### Circuit Diagram